Circuits from the Lab®リファレンス・デザインは、今日のアナログ、ミックスド・シグナル、RF設計の課題を解決するために、迅速かつ容易にシステムを統合できるように設計、テストされています。

CIRCUIT FUNCTIONS AND BENEFITS

位相ロックループ(PLL)周波数生成回路は、基本的な FM 放送帯域の受信機、デジタル通信、航空宇宙、計測器、RADAR、電子戦など、さまざまな業界やアプリケーションで広く使用されています。PLLは、1MHz未満から数十GHz以上の無線周波数(RF)および中間周波数(IF)信号の生成に使用されます。アプリケーションの要件は多岐にわたり、PLLの設計と最適化には、消費電力、位相雑音、周波数可変範囲、周波数分解能、ロック時間などのパラメーターのトレードオフが必要です。

しばしば望ましくない性能の妥協につながる重要な設計上のトレードオフは、周波数レンジ対位相雑音性能である。広帯域電圧制御発振器(VCO)は、最適な位相雑音性能を犠牲にする代わりに、広い周波数範囲を提供します。対照的に、狭帯域VCOは、達成可能なチューニングレンジを犠牲にして位相ノイズを改善します。より広いチューニング・レンジを実現するために、複数の狭帯域VCOを多重化することは可能ですが、これは多くの場合、実用的ではありません。個々のVCOに電源を切り替え、適切なRF出力を選択するために、複雑な外部回路が必要になるからです。

関連 コンテンツ

TDDおよびFDD構成のRadioThorium

このユースケースは、ベースバンド TDD および IF モード FDD 構成のための RadioThorium モジュールの手順とプロファイル設定の概要を説明します。

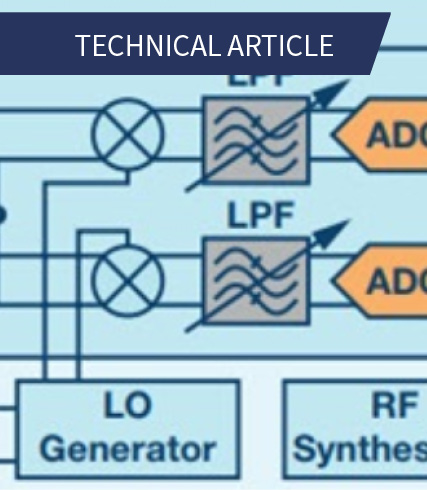

広帯域RFレシーバー・アーキテクチャ・オプションのレビュー

この記事では、ヘテロダイン受信機、ダイレクトサンプリング受信機という3つの一般的な受信機アーキテクチャの利点と課題を比較する。