Les dispositifs à large bande interdite (WBG), tels que le carbure de silicium (SiC) et le nitrure de gallium (GaN), présentent des similitudes opérationnelles avec les MOSFET et les IGBT à base de silicium, mais présentent des caractéristiques électriques distinctes qui requièrent des solutions de pilotage de grille spécialisées. Cet article explore les exigences clés de la conception de pilotes de grille isolés optimisés pour les dispositifs WBG, en soulignant les avancées critiques qui améliorent les performances, l'efficacité et la fiabilité.

auteur

Michele Sclocchi

Ingénieur d'application énergie et puissance

Europe du Sud et Israël

Exigences en matière d'isolement

Les dispositifs SiC sont conçus pour fonctionner à des tensions élevées pendant de longues périodes. Un pilote de grille isolé garantit que le circuit de commande est protégé de ces hautes tensions, ce qui améliore la fiabilité et la sécurité globales du système.

Chaque composant de sécurité a un profil de claquage diélectrique dépendant du temps. Les fabricants de composants isolés fournissent généralement des normes de certification et des données sur le profil d'isolement.

La tension de tenue à l'isolement (VISO) est définie par la tension maximale de tenue à l'isolement pendant une minute, avec une valeur typique de 5,0 kVrms/1 min.

L'isolation maximale en service (VIOWM) est la tension d'isolation maximale que l'appareil peut utiliser en continu, généralement avec une durée de vie prévue supérieure à 23 ans.

La figure 1 ci-dessous montre la durée de vie du produit isolé à 5 kVrms de Skyworks à différentes tensions de fonctionnement ; à 1 kVrms, la durée de vie prévue est de 100 ans.1

L'isolation maximale contre les surtensions (VIOSM) est destinée à simuler la foudre. Il s'agit de l'essai d'isolation haute tension le plus rigoureux, au cours duquel une forme d'onde d'impulsion de surtension prédéfinie de 10 kV est appliquée directement au composant.

Les normes industrielles spécifient également des exigences minimales d'espacement entre les contacts métalliques qui sont externes aux dispositifs d'isolation. Le cheminement est défini comme la distance mesurée le long de la surface, et l'espacement est la distance la plus courte entre deux fils conducteurs.

Les lignes de fuite et les distances minimales sont définies par les organismes de normalisation de la CEI à titre indicatif, afin d'éviter la formation d'arcs électriques pendant le fonctionnement. Ils dépendent de la tension de fonctionnement, du groupe de matériaux, de la classe et de la technologie, de l'environnement, de l'altitude et de la pollution, ainsi que de l'utilisation de l'équipement.

Certaines applications nécessitent également des isolations renforcées, obtenues en utilisant deux niveaux d'isolation en série. Cela signifie qu'en cas de défaillance d'une couche, la seconde couche offre toujours une protection de sécurité. Les isolateurs renforcés sont des dispositifs qui fournissent une isolation équivalente à deux isolateurs de base en série.

Le tableau 1 ci-dessous résume les spécifications de tension d'isolement typiques des pilotes isolés généralement proposés pour les applications SiC et GaN.

Figure 1 : Isolateur numérique Skyworks Si86xxxD, claquage diélectrique en fonction du temps

Les progrès constants dans la technologie des pilotes de grille isolés sont essentiels pour l'intégration réussie des dispositifs WBG, ouvrant la voie à des systèmes d'électronique de puissance plus efficaces et plus fiables.

Fabricant | Numéro de pièce | Niveau d'isolation | Tension de fonctionnement | Isolation renforcée | Ligne de fuite minimale | Tension de sortie maximale |

|---|---|---|---|---|---|---|

V eff. | V (crête) | V (crête) | mm | V | ||

ADI | ADuM4146 | 5000 | 2150 | 8 | 30 | |

ADI | ADuM4121 | 5000 | 849 | 558 | 8 | 35 |

Skyworks | Si8281/2/3/4 | 5000 | 1400 | 840 | 8 | 30 |

Skyworks | Si8285 | 5000 | 1400 | 840 | 8 | 30 |

onsemi | NCD57084 | 2500 | 1200 | P | 8 | 36 |

onsemi | NCD57100 | 5000 | 1000 | P | 8 | 36 |

onsemi | NCP51752 | 3500 | 870 | P | 4 | 33 |

Skyworks | Si827x | 2500 | 849 | 155 | 3.9 | 30 |

Skyworks | Si82Fx | 6000 | 1860 | 849 | 8 | 30 |

ADI | MAX2270x | 5000 | 1000 | 8 | 28 |

Tableau 1 : Spécifications typiques de la tension d'isolement des circuits d'attaque isolés pour les applications SiC et GaN

Exigences en matière de tension d'alimentation2

La transconductance d'un MOSFET est un paramètre important pour déterminer les temps de commutation, car elle influence la tension grille-source du plateau de Miller pendant la commutation.

La transconductance (gfs) est définie comme le rapport entre la variation du courant de drain et la variation de la tension de grille. Les MOSFET en carbure de silicium ont une transconductance relativement plus faible que les MOSFET en silicium (typiquement 2,6 S contre 15-20 S, respectivement). Pour compenser cette transconductance plus faible et obtenir une variation importante du courant de drain, une tension grille-source plus élevée est appliquée.

En outre, les MOSFET SiC ont tendance à rester dans la région ohmique sur une plus grande plage de Vgs, il est donc important d'avoir une transition rapide pour minimiser les pertes.

Les MOSFET SiC disponibles sur le marché sont classés en fonction de leur tension de seuil (VTH). Les MOSFET SiC à haut seuil ont des valeurs typiques supérieures à 3,5 V ; les MOSFET SiC à bas seuil ont des valeurs typiques comprises entre 3 V et 3,5 V. La tension de seuil peut varier en fonction de la température, descendre jusqu'à 1,8 V ou monter jusqu'à 4,3 V.

Dans les configurations à double extrémité (MOSFETs côté haut et côté bas), où des décharges peuvent se produire, une polarisation négative de la grille est recommandée pour fournir une marge de sécurité suffisante et empêcher les allumages parasites, en particulier à des fréquences de commutation élevées.

La tension de commande de la grille est déterminée en évaluant les facteurs de performance tels que les pertes de conduction (Rdson) et les pertes de commutation dans le cadre des valeurs recommandées pour la tension de la grille du SiC.

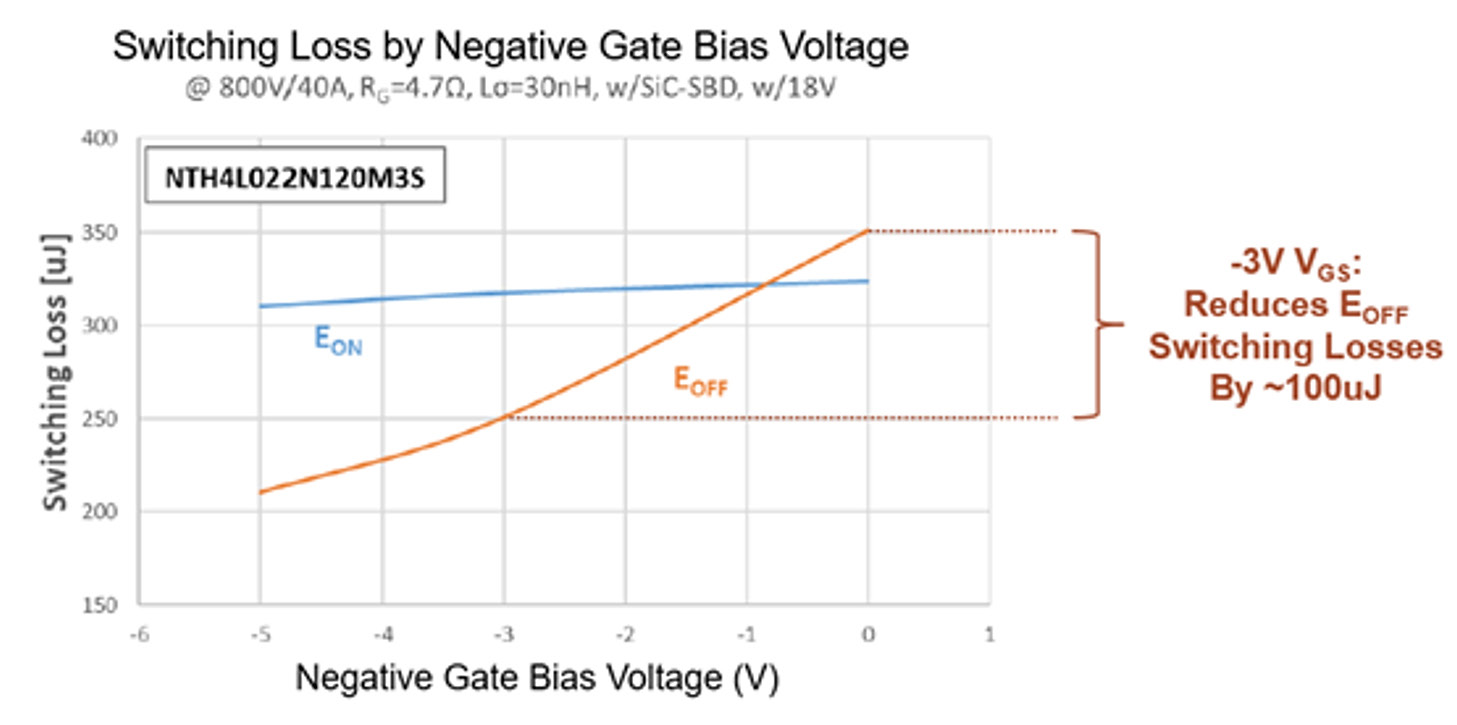

La figure 2 montre la tension de désactivation de la polarisation négative de 0 V à -5 V (axe x) et les pertes de commutation (uJ) (axe y). Il est à noter que la tension de coupure de -3 V réduit les pertes de commutation (Eoff) de 25 %.

Figure 2 : Perte de commutation ONSEMI SiC en fonction de la tension de polarisation négative de la grille (source ONSEMI ND90204/D)

Verrouillage en cas de sous-tension (UVLO)

Le verrouillage par sous-tension est une fonction conçue pour protéger les systèmes en cas de défaillance de l'alimentation de polarisation. Le circuit UVLO surveille en permanence la tension d'alimentation de la porte et désactive la porte si la tension tombe en dessous d'un seuil défini.

Les pilotes en carbure de silicium nécessitent généralement un seuil UVLO plus élevé que les dispositifs en silicium. Les pilotes de grille SiC dédiés comprennent souvent des niveaux UVLO programmables ou des options prédéfinies, avec des seuils allant de 10 V à 16 V. L'UVLO doit être fixé bien au-dessus de la région du plateau de Miller (8-9 V) et aligné sur les capacités thermiques du dispositif SiC.

La figure 3 illustre les caractéristiques typiques à l'état passant d'un MOSFET SiC à différents niveaux de tension porte-source (Vgs). Si le système fonctionne à 150 A avec une tension de grille nominale de 20 V et que l'UVLO est réglé sur 15 V, la chute de tension entre le drain et la source (Vds) est réduite à une fraction minime de volt (du point A au point B).

Toutefois, si l'UVLO est réglé en dessous de 12 V, la protection thermique devient insuffisante, ce qui entraîne une chute de tension plus de deux fois supérieure au niveau attendu (point C).

Figure 3 : Tension de chute à l'état passant d'un dispositif MOSFET SiC à différents niveaux de tension de grille

Courant de crête du conducteur3

Le courant de crête est souvent mis en évidence dans les fiches techniques des circuits d'attaque, mais sa définition peut varier d'un fabricant à l'autre. Généralement, les fiches techniques définissent le courant de crête comme le courant de saturation, mesuré en court-circuitant la sortie vers une grande capacité ou en pulsant brièvement le circuit d'attaque dans un court-circuit. Cependant, les courbes I-V détaillées indiquant les valeurs minimales et maximales à différentes températures et variations de fabrication sont rarement incluses.

Une autre définition du courant de crête consiste à spécifier le courant maximal dans la région linéaire de la courbe I-V la plus basse. Cette approche conservatrice garantit que les FET de sortie du circuit d'attaque de grille ne saturent pas quelles que soient les conditions de température et de processus, à condition que la résistance de grille externe soit correctement dimensionnée.

Au-delà de la valeur du courant de crête, il est important de prendre en compte des spécifications telles que la résistance de source et de puits des commutateurs internes et les temps de montée et de descente dans des conditions spécifiques. Par exemple, la résistance des commutateurs internes pull-up et pull-down a un impact significatif sur le courant moyen et la dissipation de puissance dans le pilote et la résistance de grille externe.

Le tableau 2 résume la tension, le courant et la vitesse de divers pilotes de grille isolés, en soulignant les options qui conviennent aux applications SiC typiques.

Fabricant | Numéro de pièce | Tension de sortie maximale | I out peak (Source/Sink) | Résistance Rout (Source/Sink) | Temps de montée/descente de la sortie | Délai de propagation (ns) |

|---|---|---|---|---|---|---|

V | A | Ω | nS | nsec | ||

ADI | ADuM4146 | 30 | 11 | 0.6 | 18 | 44 |

ADI | ADuM4121 | 35 | 2 | 1.8/1.6 | 18 | 53 |

Skyworks | Si8281/2/3/4 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 50 |

Skyworks | Si8285 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 40 |

onsemi | NCD57084 | 36 | 7 | 10 | 60 | |

onsemi | NCD57100 | 36 | 7 | 15 | 70 | |

onsemi | NCP51752 | 33 | 4.5/9 | 1.4/0.5 | 15/8 | 36 |

Skyworks | Si827x | 30 | 1.8/4.0 | 2.7/1.0 | 10/13 | 45 |

Skyworks | Si82Fx | 30 | 4 | 0.7 | 15 | 30 |

ADI | MAX2270x | 28 | 4/5.7 | 1.25 | 3.6/2.5 | 5 |

Immunité aux transitoires en mode commun (CMTI) et capacité d'isolation4

L'immunité aux transitoires en mode commun (CMTI) est un facteur clé dans le choix des pilotes de grille isolés. L'immunité aux transitoires en mode commun (CMTI) est un facteur clé dans le choix d'un circuit d'attaque de grille isolé. En règle générale, la valeur CMTI d'un circuit d'attaque de porte isolé doit dépasser la vitesse de commutation maximale des dispositifs SiC. Avec une vitesse de commutation typique de 50 V/nS, la valeur CMTI doit être supérieure à 100 V/ns. Bon nombre des dernières générations de circuits d'attaque isolés en SiC et GaN ont des valeurs CMTI supérieures à 200 kV/uS.

Les dispositifs à commutation rapide comme le SiC et le GaN avec des pilotes de grille à faible CMTI peuvent rencontrer divers problèmes, tels que des défauts, des impulsions manquées, un délai de propagation accru et un temps mort prolongé.

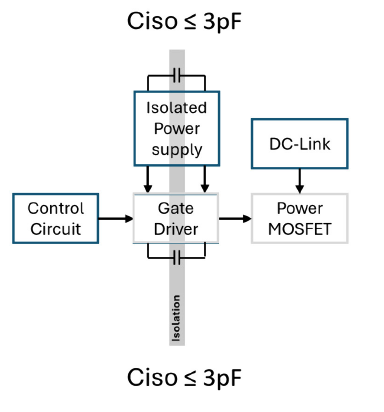

Un autre facteur important à prendre en compte est la capacité d'isolation parasite (Ciso), généralement mesurée en quelques picofarads entre la broche de contrôle d'entrée et la sortie. Dans une application SiC avec un taux de transition rapide de 100 V/ns et une capacité d'isolation de 2 pF, cela peut se traduire par un courant de 200 mA traversant la limite d'isolation.

Tableau 3 : Résumé du CMTI typique et de la capacité d'isolation des pilotes isolés pour les dispositifs SiC et GaN

Cette considération s'applique également aux convertisseurs DC-DC isolés utilisés pour fournir les tensions de grille positive et négative au dispositif. Il est important de choisir des convertisseurs conçus pour les applications SiC et GaN avec une très faible capacité d'isolation entre le primaire et le secondaire. Par exemple, la nouvelle famille de convertisseurs DC-DC isolés de RECOM (R12C2T25/R) présente une capacité d'isolation inférieure à 3,5 pF.

Pince de Miller active

Des courts-circuits peuvent se produire dans les moteurs et autres systèmes d'électronique de puissance, ce qui fait de la robustesse des MOSFET SiC une préoccupation majeure dans ces applications. Dans des conditions de surintensité, les MOSFET SiC doivent simultanément gérer des courants importants et des tensions de bus DC élevées pendant une durée suffisamment longue, jusqu'à ce que les circuits de protection contre les courts-circuits s'activent et que le signal de commande de la grille éteigne le dispositif.

L'énergie critique (Ec), une mesure essentielle de la robustesse des dispositifs de puissance, fait référence à la quantité minimale d'énergie dissipée qui entraîne la défaillance du dispositif testé après un seul court-circuit.

Les fabricants d'appareils spécifient généralement une capacité de résistance aux courts-circuits, c'est-à-dire la durée pendant laquelle un appareil peut supporter un court-circuit avant d'être endommagé.

Le courant de court-circuit est limité par Vds/Rdson et le courant de saturation du dispositif, le plus petit des deux étant retenu.

Selon la littérature, un MOSFET SiC de 1200 V peut résister à un court-circuit de 5-14 μs sous une tension de bus de 600 Vdc et une commande de grille de 20 V à température ambiante, ce qui est nettement moins bon que les IGBT Si équivalents.

Comme les dispositifs SiC et GaN ont de petites matrices, la densité de courant plus élevée provoque une augmentation plus rapide de la température par rapport aux dispositifs Si standard, ce qui se traduit par un temps de défaillance plus court et nécessite des temps de protection plus rapides.

La figure 5 compare le comportement en court-circuit de deux dispositifs de commutation différents ayant la même tension et le même courant nominal. Le temps de résistance au court-circuit de l'IGBT (courbe violette) est d'environ 38 microsecondes, contre 8 microsecondes pour le dispositif SiC équivalent (courbe rouge). Le courant de court-circuit de pointe de l'IGBT peut atteindre 200 ampères, alors qu'il est presque le double pour le dispositif SiC.

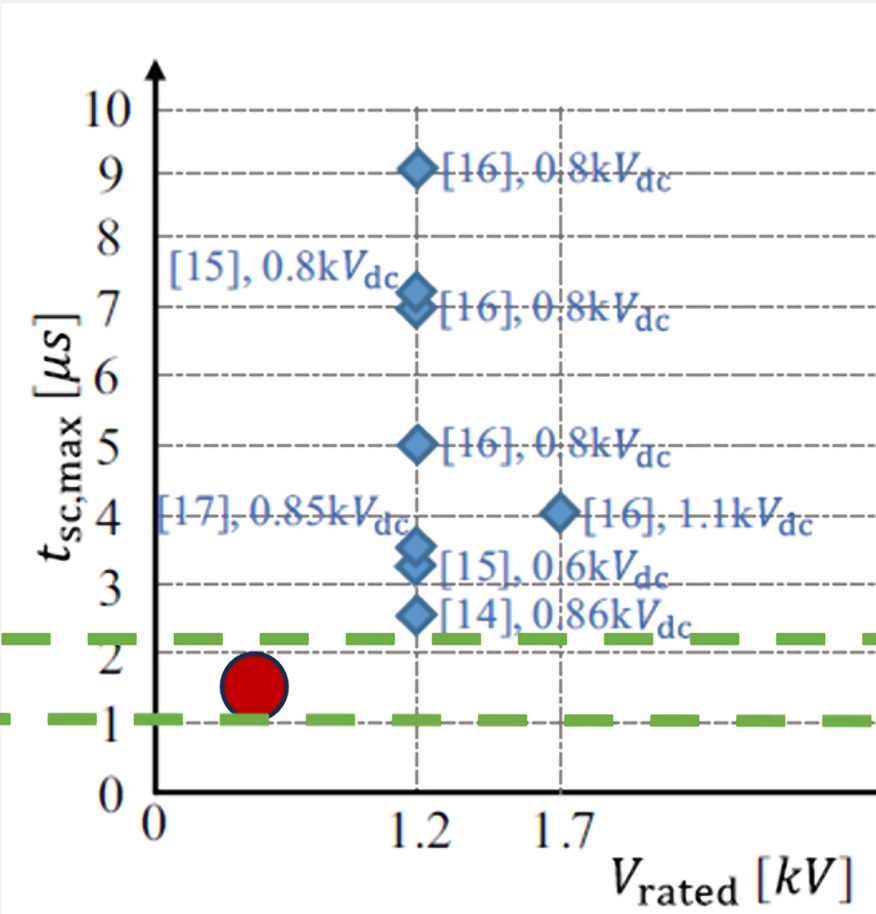

La protection contre les courts-circuits mise en œuvre dans le circuit d'attaque doit avoir un temps de réponse nettement plus rapide que le temps de résistance maximal aux courts-circuits du dispositif SiC. La figure 6, ci-dessous, résume le temps de réponse maximal aux courts-circuits des modules SiC en fonction de leur tension nominale entre le drain et la source avec la tension de liaison continue indiquée en cours d'essai. Un temps de réponse aux courts-circuits inférieur à 2 μs est relativement sûr pour un seul événement de court-circuit. En général, le temps de réponse aux courts-circuits augmente avec la surface du dispositif et la longueur du canal du MOSFET.6

Plus le temps de réponse aux courts-circuits est court, plus la capacité du dispositif à résister à des courts-circuits multiples est grande. Cependant, il n'existe pas de valeur fixe universelle pour le temps de résistance aux courts-circuits ; il varie en fonction de facteurs tels que le bus de tension, les caractéristiques du boîtier et la surface du boîtier. Par exemple, un MOSFET SiC dans un boîtier TO-247 a un temps de résistance aux courts-circuits de 1,7 μs à 800 V et d'environ 10 μs à 400 V.

La figure 7 résume le temps de défaillance des différents types de transistors de puissance en fonction de la tension du bus continu. Il convient de noter que les temps de défaillance des GaN HEMT en mode E sont beaucoup plus courts que ceux des MOSFET en Si et SiC.

Le temps de résistance au court-circuit mesuré d'un GaN de 650 V, fonctionnant à un bus de tension continue de 400 V, est d'environ 630 nsec.

Le temps de résistance aux courts-circuits peut être calculé à l'aide de l'énergie critique (Ec) :

Figure 5 : Comparaison du courant de court-circuit du MOSFET SiC 1200 V/40 A et de l'IGBT Si 1200 V/40 A sous Vds = 600 V et Tc = 25°C4

Figure 6 : Temps de réponse aux courts-circuits (SCRT) des modules SiC

Figure 7 : Temps de défaillance de différents types de transistors de puissance

Comportement typique en court-circuit d'un MOSFET SiC

La figure 8 montre les formes d'ondes de court-circuit typiques d'un test non destructif à faible inductance. Un SiC 1200 V planaire, avec un bus DC limité à 400 Vdc, subit un test de court-circuit à faible inductance (60 nH) à l'aide d'une impulsion de court-circuit de 2,2 μs pour assurer la survie du dispositif. Les formes d'onde peuvent être visualisées en quatre phases :

- Phase A : Le MOSFET SiC passe de la région de coupure à la région ohmique. Le courant commence à augmenter rapidement en raison de la faible inductance de la boucle. Dans ce cas, le di/dt est d'environ 4 A/ns, ce qui se traduit par un courant pouvant atteindre 1 kA en 1 μs. À 1,1 μs, à la fin de la phase A, l'énergie de court-circuit est d'environ 0,4 J, ce qui dépasse la limite de dissipation maximale du dispositif. Par conséquent, la protection contre les courts-circuits

doit être activée avant que le dispositif n'entre dans la zone de saturation. - Phase B : le MOSFET SiC entre dans la zone de saturation et l'énergie de court-circuit continue d'augmenter.

- Phase C : Le MOSFET SiC reste dans la région de saturation. L'augmentation de Rds,on entraîne une baisse de Id par rapport à son pic.

- Phase D : Lorsque le MOSFET SiC est désactivé (lorsque la protection est activée), le dI/dt élevé (33 A/ns) induit un dépassement de la tension de crête

de 2,2 kV.

La protection contre les courts-circuits doit être activée dans la zone verte (linéaire), généralement dans un délai de 1 à 2 μs. Lorsque le court-circuit est détecté, le MOSFET doit être désactivé avec une vitesse de balayage contrôlée (fonction de commutation douce) pour minimiser les dépassements.

La figure 9, ci-dessous, illustre le temps de résistance des MOSFET SiC planaires 700 V de Microchip en fonction de la tension grille-source et du bus de tension continue. Comme on pouvait s'y attendre, le temps de tenue augmente lorsque Vgs est réduite. Cela permet de mieux contrôler la coupure du MOSFET SiC après la détection d'un court-circuit afin de minimiser le dépassement (coupure en douceur). Les disjoncteurs à semi-conducteurs (SSCB) ou les fusibles E constituent une application notable où la durée de vie supérieure des MOSFET SiC planaires de Microchip est très appréciée.8

Figure 8 : Comportement typique d'un MOSFET SiC en court-circuit7

Figure 9 : Les MOSFET SiC de Microchip présentent des temps de résistance aux courts-circuits compris entre 3 μs et 14 μs, en fonction de la tension de liaison continue et de la Vgs appliquée.

Circuit de protection DESAT9

Un circuit de désaturation (DESAT) est une méthode largement utilisée pour la protection contre les surintensités et les courts-circuits dans les circuits IGBT. Il surveille la tension entre le drain et la source lorsque le dispositif est entièrement activé et l'arrête automatiquement si un court-circuit ou une surintensité est détecté.

Les pilotes de grille isolés avec circuits DESAT intégrés, conçus à l'origine pour les IGBT, peuvent également être utilisés avec des MOSFET SiC et des dispositifs GaN.

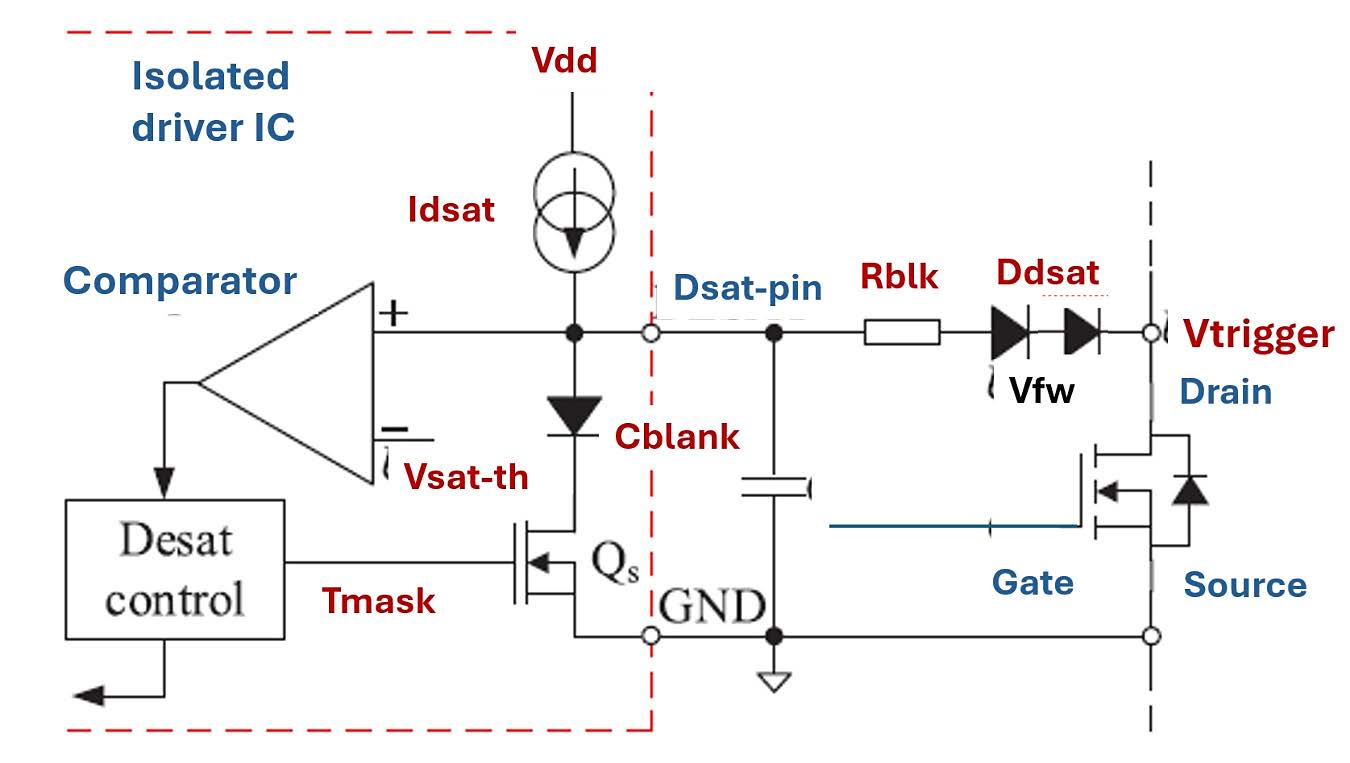

Généralement, comme le montre la figure 10, le circuit DESAT est intégré dans le circuit d'attaque de grille, ne nécessitant que quelques composants externes - une diode haute tension rapide (Ddsat) ou plusieurs diodes en série, un condensateur d'effacement (Cblank) et une résistance (Rblk).

Lorsque le MOSFET s'allume, une source de courant (Idsat) charge le condensateur, ce qui crée une période d'attente pour éviter les déclenchements intempestifs pendant la commutation. La diode est polarisée vers l'avant une fois que la tension du condensateur correspond à la tension entre le drain et la source du MOSFET. Un court-circuit est déclenché lorsque la tension drain-source du MOSFET (Vds) atteint le seuil de protection (Vth-dsat), moins la chute de tension directe de la diode et la tension à travers la résistance en série (Idsat × Rdsat).

Figure 10 : Circuit de protection DESAT typique couramment utilisé dans les pilotes de grille pour les IGBT et les MOSFET SiC afin de les protéger contre les surintensités et les courts-circuits.

L'ajustement de la valeur de la résistance ou l'utilisation de plusieurs diodes en série peut modifier la tension de déclenchement.

En général, le point de déclenchement de la DESAT est fixé à deux fois le courant de crête maximal, mais il doit être soigneusement ajusté au courant maximal souhaité lors d'un court-circuit.

La diode DESAT doit être de type à récupération rapide avec une faible capacité de jonction pour minimiser la susceptibilité au bruit causée par des changements de tension rapides (dv/dt).

Le temps d'arrêt est configuré pour éviter les faux déclenchements pendant la phase d'allumage du MOSFET et pour permettre aux oscillations d'allumage de se stabiliser. La tension de déclenchement (Vtrigger) et le temps d'arrêt doivent être réglés avec précision en fonction des caractéristiques spécifiques et du comportement à la mise sous tension du MOSFET SiC.

Il est essentiel de veiller à ce que l'énergie totale pendant un court-circuit reste inférieure à un quart de l'énergie de résistance maximale spécifiée par le fabricant de SiC.

Le circuit DESAT est simple, facile à mettre en œuvre et présente une perte de puissance minimale. Cependant, il présente certains défis lorsqu'il est utilisé avec des MOSFET SiC. La diode directe doit résister à des tensions élevées et réagir rapidement, et le temps de suppression fixe peut retarder la réponse de la protection contre les courts-circuits

.

Il est important de noter que la méthode DESAT peut ne pas fournir une précision constante dans toutes les conditions de défaut. Différents scénarios de défaillance, tels que les défaillances à commutation dure ou les défaillances sous charge, peuvent entraîner des temps de réponse variables. Néanmoins, l'objectif premier est d'éviter une défaillance catastrophique du dispositif, même en présence de surtensions rapides à faible inductance.

Par exemple, lors de la protection d'un module SiC typique, une simple variation de 0,5 V de la tension de seuil DESAT peut correspondre à une différence allant jusqu'à 100 A dans le courant de drain.

Temps de réponse aux défauts pour les MOSFET SiC

Le temps de réponse aux courts-circuits (SCRT) doit être limité à 1 μs pour les MOSFET SiC. Le temps de réponse total de la protection, tel qu'illustré à la figure 11, est la somme de quatre composantes :

- t_mask: Temps fixe pendant lequel la broche DESAT est intentionnellement maintenue basse (connectée à la masse) pour éviter un faux déclenchement du circuit de protection dû à des pics de tension pendant la mise sous tension initiale du MOSFET SiC. Ce temps est généralement compris entre 200 et 300 ns.

- t_blank: Temps de charge du condensateur C_blank par la source de courant interne ou une résistance externe.

- t_filter: Délai interne typique entre le moment où la tension DESAT atteint son seuil et l'émission de la commande de désactivation de la grille du MOSFET.

- t_soft: Le temps d'arrêt progressif, qui est ajouté pour réduire le risque de pointes de surtension pendant le processus de désactivation du MOSFET SiC.

La forme d'onde illustrée à la figure 12 ci-dessous a été capturée sur un banc lors d'un scénario de défaut hard-switched, où le MOSFET s'allume dans une condition de défaut. Dans ce cas, le temps de suppression ajoute le temps total de détection du défaut, suivi par le temps de rampe, qui est généralement défini par une résistance d'excursion haute chargeant un condensateur externe. Cette rampe se poursuit jusqu'à ce que la tension atteigne le seuil, ce qui déclenche la séquence d'arrêt progressif.

La trace jaune inférieure montre l'augmentation de la tension porte-source et, lorsque la protection contre les courts-circuits est activée, elle passe en mode d'arrêt progressif.

Comme indiqué précédemment, la réaction totale du circuit DESAT doit être comprise entre 1 et 2 usec. Pour accélérer le temps de détection sans compromettre l'immunité au bruit de la broche Dsat, il est possible d'augmenter le courant de charge interne du condensateur Cblank en ajoutant une source de courant externe (

). Pour maintenir une bonne immunité au bruit, le condensateur Cblank doit avoir une valeur supérieure à 300 pF.

La figure 13 montre la configuration du circuit externe qui peut être utilisée pour obtenir un temps de charge plus rapide pour le condensateur Cblank, sans réduire sa valeur de capacité. Cette solution peut également être mise en œuvre pour les dispositifs GaN en cascade, ce qui permet d'obtenir un temps de réponse total inférieur à 400 ns.12

La figure 14 ci-dessous montre un circuit discret de protection contre les courts-circuits optimisé pour une détection et une protection rapides, spécialement conçu et testé pour les dispositifs GaN HEMT. Ce circuit a été testé avec un temps de réponse total de 122 ns.13

Le principe de base consiste à mesurer Vds-on à travers le dispositif à l'état passant (Vsense) et à la comparer à une tension de référence. Si Vsense dépasse Vref, le comparateur émet un signal de défaut élevé (FLT). Le signal d'arrêt est utilisé pour réinitialiser la tension Vsense.

Si un pilote isolé est utilisé, le signal FLT peut être renvoyé au pilote par l'intermédiaire d'un isolateur. Le signal FLT envoyé au circuit d'attaque peut désactiver le circuit d'attaque de la grille, ce qui force la mise hors tension du dispositif GaN. Les circuits d'attaque isolés avec un temps de propagation court sont préférables pour obtenir des temps de réponse ultrarapides.

Figure 11 : Temps de réponse de la protection totale

Figure 12 : Scénario de défaut de commutation dur d'un module SiC avec pilote de grille isolé d'Analog Devices.11 Le temps de réponse total est maintenu en dessous de 1 μs.

Figure 13 : Configuration du circuit externe pour un temps de charge plus rapide du condensateur Cblank, sans réduction de la valeur de la capacité

Figure 14 : Temps de réponse ultra-rapide pour les dispositifs GaN HEMT13

Exigences en matière de courant de porte et dissipations de puissance

Pour atteindre la vitesse de commutation souhaitée, il est essentiel de choisir un circuit d'attaque de grille avec une capacité de courant d'attaque appropriée.

Le courant de crête de la source et du puits peut être facilement calculé en divisant la tension appliquée à la borne porte-source (dVgdr) par la somme des résistances du chemin :

Rgin représente la résistance interne de la grille du MOSFET SiC, Rgonext et Rgoffext sont les résistances externes de la grille utilisées pour contrôler les vitesses d'activation et de désactivation. De même, Rgondriver et Rgoffdriver représentent la résistance interne du pilote de grille.

Pour que les résistances externes puissent réguler efficacement les vitesses de commutation, les courants de source et de fuite restent dans les limites de courant de crête du circuit d'attaque.

To improve heat dissipation and boost gate peak current in high-frequency or high-current SiC applications, an external totem pole bipolar transistor is recommended.

La figure 15, ci-dessous, illustre un circuit de base d'amélioration de l'entraînement pour le circuit d'attaque isolé Si828x de Skyworks. Bipolar transistors Q1 and Q2 regulate the driver current, controlled by the VH and VL signals. L'image de droite illustre un courant de source maximal de 30 A avec une capacité de grille de 220 pF.

En particulier dans les applications de grands modules, le circuit totem externe permet d'optimiser la disposition et les performances en permettant aux transistors d'être placés plus près de la grille du MOSFET. Cela minimise l'inductance du circuit de la grille et réduit la sonnerie potentielle au niveau de la broche de la grille du dispositif. De plus, le circuit externe évite de dépasser la capacité maximale de dissipation de puissance du circuit d'attaque.

La puissance totale requise pour le circuit de la grille est déterminée en multipliant la charge totale de la grille (Qg) du MOSFET SiC par la tension appliquée à la borne grille-source (dVgdr) et la fréquence de commutation (fsw) :

Conclusion

Dans l'ensemble, les progrès continus de la technologie des pilotes de grille isolés sont essentiels pour l'intégration réussie des dispositifs WBG dans diverses applications, ouvrant la voie à des systèmes d'électronique de puissance plus efficaces et plus fiables.

Références

(*1) AN583 Safety Considerations and Layout Recommendations for Digital Isolators - Skyworks

(*2) ND90204 EliteSiC Gen 2 1200V MOFETs application note - ONSEMI

(*3) Peak Current of Isolated Gate Driver - Analog Devices

(*4) Review and analysis of SIC MOSFET's ruggdness and reliability - Jun Wang, Xi Jiang - Feb 2020

(*5) AN5355 Mitigation techniques of the SIC MOSFET gate voltage glitches with Miller clamp

(*6) Comparison and Discussion on Short-circuit Protection for SiC MOSFET Modules, Slavko Mocevic IEEE

(*7) Source : Nouvelle définition de l'énergie critique pour la robustesse des MOSFET SiC en cas de court-circuit.

(*8) SiC-Based Auxiliary E-Fuse Technology Demonstrator for EV Applications - Microchip - PCIM Europe

(*9) AN1288 : Si828x External Enhancement Circuit - Skyworks An improved desaturation short-circuit protection method for SiC power modules science direct

(*10) An improved desaturation short-circuit protection method for SiC power modules science direct (CPESE 2021)

(*11) Wolfspeed- Analog Device - Isolated Gate driver seminar

(*12) AN1288 : Si828x External Enhancement Circuit- Skyworks

(*13) A Simple Desaturation Based Protection Circuit for GaN HEMT With Ultrafast response time - IEEE June 2021

(*14) AN1288 Si828x External Enhancement Circuit - Skyworks DN80 - Bipolar transistors for MOSFET gate driving applications - Diodes