炭化ケイ素(SiC)や窒化ガリウム(GaN)などのワイドバンドギャップ(WBG)デバイスは、シリコンベースのMOSFETやIGBTと動作面で類似しているが、特殊なゲートドライブ・ソリューションを必要とする明確な電気的特性を示す。この記事では、WBGデバイスに最適化された絶縁型ゲート・ドライバを設計するための重要な要件を探り、性能、効率、信頼性を向上させる重要な進歩に焦点を当てます。

著者

ミケーレ・スクロッキ

Energy & Power Application Engineer

南ヨーロッパ & イスラエル

絶縁要件

SiCデバイスは、長期間にわたって高電圧で動作するように設計されています。絶縁ゲート・ドライバは、制御回路をこれらの高電圧から確実に保護し、システム全体の信頼性と安全性を高めます。

全ての安全部品には時間依存性の絶縁破壊プロファイルがあります。絶縁部品のメーカーは通常、認証規格と絶縁プロファイルのデータを提供しています。

絶縁耐電圧(VISO)は、1分間の最大耐電圧で定義され、標準値は5.0 kVrms/1分です。

最大使用絶縁(VIOWM)は、デバイスが連続的に動作可能な最大絶縁電圧で、通常23年以上の寿命が期待されます。

以下の図1は、Skyworksの5 kVrmsの絶縁製品の、異なる使用電圧における電圧寿命を示しています。

最大サージ絶縁定格(VIOSM)は雷状態をシミュレートすることを目的としています。これは最も厳しい高電圧絶縁試験で、10kVの定義済みサージパルス波形が部品に直接印加されます。

業界標準では、絶縁デバイスの外部にある金属接点間の最小間隔要件も規定しています。クリープは表面に沿って測定した距離、クリアランスは2本の導電性リード間の最短距離と定義されています。

最小沿面距離とクリアランスは、動作中のアーク放電を防止することを目的としたガイダンスとして、IEC規格団体によって定義されています。これらは、使用電圧、材料グループ、クラスおよび技術、環境への配慮、高度および汚染、機器の使用状況によって異なります。

アプリケーションによっては、2つの絶縁レベルを直列に使用することで強化された絶縁を必要とするものもあります。これは、1つのレイヤーが故障しても、2番目のレイヤーが安全保護を提供することを意味します。強化アイソレータは、2つの基本アイソレータを直列に接続したのと同等の絶縁を提供するデバイスです。

以下の表 1 は、SiC および GaN アプリケーションに一般的に推奨される絶縁ドライバの標準的な絶縁電圧仕様をまとめたものです。

図1: Skyworksデジタル・アイソレータSi86xxxDの時間依存型絶縁破壊

絶縁ゲート・ドライバ技術の継続的な進歩は、WBGデバイスの統合を成功させ、より効率的で信頼性の高いパワー・エレクトロニクス・システムへの道を開くために不可欠である。

メーカー | 品番 | 断熱等級 | 使用電圧 | 強化絶縁 | 最小クリープ | 最大出力電圧 |

|---|---|---|---|---|---|---|

V rms | V(ピーク) | V(ピーク) | mm | V | ||

ADI | ADuM4146 | 5000 | 2150 | 8 | 30 | |

ADI | ADuM4121 | 5000 | 849 | 558 | 8 | 35 |

スカイワークス | Si8281/2/3/4 | 5000 | 1400 | 840 | 8 | 30 |

スカイワークス | Si8285 | 5000 | 1400 | 840 | 8 | 30 |

オンセミ | NCD57084 | 2500 | 1200 | P | 8 | 36 |

オンセミ | NCD57100 | 5000 | 1000 | P | 8 | 36 |

オンセミ | NCP51752 | 3500 | 870 | P | 4 | 33 |

スカイワークス | Si827x | 2500 | 849 | 155 | 3.9 | 30 |

スカイワークス | Si82Fx | 6000 | 1860 | 849 | 8 | 30 |

ADI | MAX2270x | 5000 | 1000 | 8 | 28 |

表1:SiCおよびGaNアプリケーション用絶縁型ドライバーの代表的な絶縁電圧仕様

駆動電圧要件2

MOSFETのトランスコンダクタンスは、整流時のミラー・プラトー電圧に影響するため、スイッチング時間を決定するための重要なパラメータである。

トランスコンダクタンス(gfs)は、ゲート電圧の変化に対するドレイン電流の変化の比率として定義される。シリコンカーバイドMOSFETは、シリコンMOSFETに比べてトランスコンダクタンスが相対的に低い(それぞれ通常2.6S対15~20S)。この低いトランスコンダクタンスを補い、ドレイン電流を大きく変化させるためには、高いゲート・ソース間電圧が印加される。

さらに、SiC MOSFETは、より広いVgs範囲にわたってオーミック領域に留まる傾向があるため、損失を最小限に抑えるためには、高速なトランジションが重要である。

市場で入手可能なSiC MOSFETは、しきい値電圧(VTH)によって分類される。高しきい値は3.5 Vを超える典型的な値であり、低しきい値SiC MOSFETの典型的な値は3 Vから3.5 Vである。しきい値電圧は温度によって変化し、1.8Vまで下がったり、4.3Vまで上がったりする。

シュートスルーが発生する可能性のあるダブルエンド構成(ハイサイドとローサイドのMOSFET)では、十分な安全マージンを確保し、特にスイッチング周波数が高い場合に寄生ターンオンを防止するため、負のゲートバイアスを推奨する。

動作ゲート駆動電圧は、SiCゲート電圧推奨値の範囲内で、伝導損失(Rdson)やスイッチング損失などの性能要因を評価して決定される。

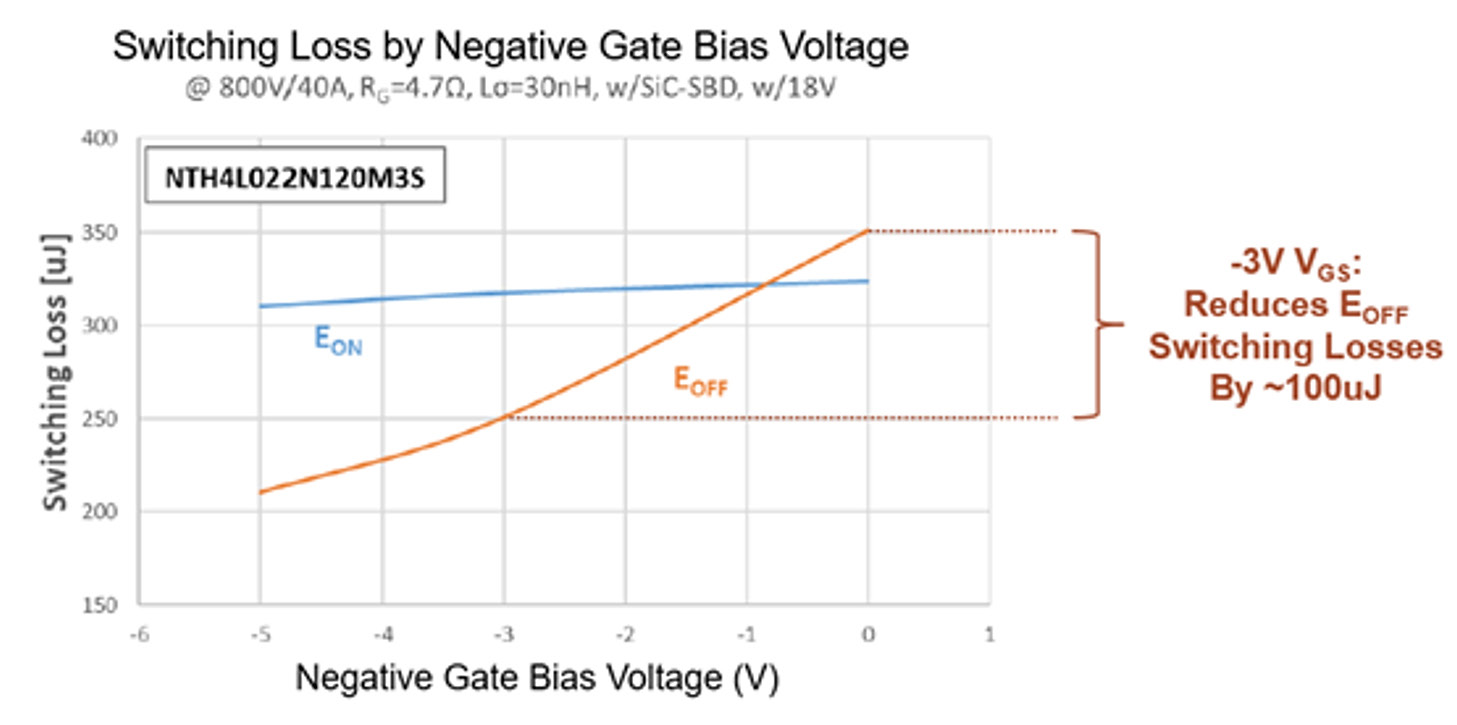

図 2 は、0 V から -5 V までの負バイアスのターンオフ電圧(x 軸)とスイッチング損失(uJ)(y 軸)を示している。ターンオフを-3 Vで駆動すると、スイッチングオフ(Eoff)損失が25%減少することに注意してください。

図 2:ONSEMI SiC スイッチング損失対負ゲートバイアス電圧(ソース ONSEMI ND90204/D)

低電圧ロックアウト(UVLO)

低電圧ロックアウトは、バイアス電源が故障した場合にシステムを保護するために設計された機能です。UVLO回路は、ゲート電源電圧を継続的に監視し、電圧が定義されたしきい値を下回った場合にゲートを無効にします。

炭化ケイ素ドライバは通常、シリコン・デバイスよりも高い UVLO しきい値を必要とする。専用の SiC ゲート・ドライバには、しきい値が 10 V~16 V のプログラマブル UVLO レベルまたは定義済みオプショ ンが含まれていることが多く、UVLO はミラー・プラトー領域(8~9 V)よりかなり上に設定し、SiC デバイスの熱能力に合わせる必要があります。

図3は、さまざまなゲート-ソース間電圧(Vgs)レベルにおけるSiC MOSFETの典型的なオン状態特性を示している。システムが公称ゲート電圧20Vで150A動作し、UVLOが15Vに設定されている場合、ドレイン・ソース間電圧降下(Vds)は(A点からB点への)最小数分の1ボルトに低減される。

しかし、UVLOが12V未満に設定された場合、熱保護が不十分となり、予想されるレベルの2倍以上の電圧降下につながる(C点)。

図3:

ゲート電圧レベルを変えた場合のSiC MOSFETデバイスのオン状態降下電圧

ドライバ・ピーク電流3

ピーク電流は、ゲート・ドライバのデータシートでしばしば強調されていますが、その定義はメーカーによって異なる場合があります。通常、データシートではピーク電流を飽和電流と定義しており、出力を大容量に短絡するか、ドライバを短時間パルス的に短絡して測定する。しかし、様々な温度や製造上のばらつきにおける最小値と最大値を示す詳細なI-V曲線が記載されていることは稀である。

ピーク電流の別の定義としては、最小のI-V曲線の線形領域内の最大電流を指定する方法がある。この保守的なアプローチにより、外付けゲート抵抗が適切なサイズであれば、ゲート・ドライバの出力FETがあらゆる温度とプロセス条件下で飽和しないことが保証される。

ピーク電流値だけでなく、内部スイッチのシンク抵抗やソース抵抗、特定条件下での立ち上がり時間や立ち下がり時間などの仕様を考慮することも重要である。例えば、内部プルアップとプルダウンスイッチの抵抗値は、ドライバと外部ゲート抵抗の平均電流と消費電力に大きく影響します。

表2は、さまざまな絶縁型ゲート・ドライバの電圧、電流、速度をまとめたもので、典型的なSiCアプリケーションに適したオプションを強調している。

メーカー | 品番 | 最大出力電圧 | Iアウト・ピーク(ソース/シンク) | ルート(ソース/シンク)抵抗 | 出力立ち上がり/立ち下がり時間 | 伝搬遅延 (ns) |

|---|---|---|---|---|---|---|

V | A | Ω | nS | エヌセック | ||

ADI | ADuM4146 | 30 | 11 | 0.6 | 18 | 44 |

ADI | ADuM4121 | 35 | 2 | 1.8/1.6 | 18 | 53 |

スカイワークス | Si8281/2/3/4 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 50 |

スカイワークス | Si8285 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 40 |

オンセミ | NCD57084 | 36 | 7 | 10 | 60 | |

オンセミ | NCD57100 | 36 | 7 | 15 | 70 | |

オンセミ | NCP51752 | 33 | 4.5/9 | 1.4/0.5 | 15/8 | 36 |

スカイワークス | Si827x | 30 | 1.8/4.0 | 2.7/1.0 | 10/13 | 45 |

スカイワークス | Si82Fx | 30 | 4 | 0.7 | 15 | 30 |

ADI | MAX2270x | 28 | 4/5.7 | 1.25 | 3.6/2.5 | 5 |

コモンモード過渡イミュニティ(CMTI)とアイソレーション・キャパシタンス4

コモンモード過渡耐性(CMTI)は、絶縁ゲート・ドライバを選択する際の重要な要素です。CMTIとは、絶縁された2つの回路間のコモンモード電圧の最大許容変化率を意味する。一般に、絶縁型ゲート・ドライバのCMTI定格は、SiCデバイスの最大スイッチング速度を上回る必要があります。典型的なスイッチング速度が50 V/nSの場合、CMTI定格は100 V/ns以上でなければなりません。最新世代の絶縁型SiCおよびGaNドライバーの多くは、CMTI値が200kV/uSを超えています。

SiCやGaNのような高速スイッチング・デバイスでは、CMTIの低いゲート・ドライバを使用すると、故障、パルスの取りこぼし、伝搬遅延の増加、デッドタイムの延長など、さまざまな問題が発生する可能性がある。

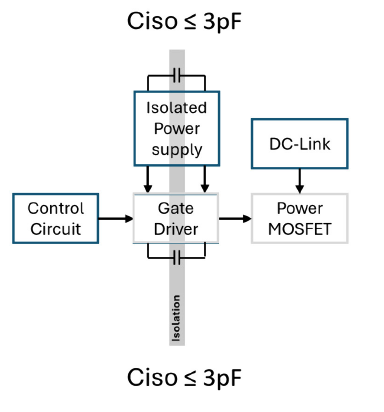

考慮すべきもう1つの重要な要因は、寄生絶縁容量(Ciso)で、通常、入力制御ピンと出力間の数ピコファラドで測定されます。100V/nsの高速遷移レートと2pFの絶縁キャパシタンスを持つSiCアプリケーションでは、絶縁境界を200mAの電流が流れることになります。

表3:SiCとGaNデバイスの絶縁型ドライバーの代表的なCMTIと絶縁容量のまとめ

この考慮は、デバイスに正負のゲート電圧を供給するために使用される絶縁 DC-DC コンバーターにも適用される。一次側と二次側の間の絶縁容量が非常に小さい、SiCおよびGaNアプリケーション用に設計されたコンバータを選択することが重要です。例えば、RECOMの絶縁型DC-DCコンバータの新ファミリー(R12C2T25/R)は、3.5pF未満の絶縁容量を特長としています。

アクティブ・ミラー・クランプ

モーター駆動やその他のパワー・エレクトロニクス・システムでは短絡現象が発生することがあり、このような用途ではSiC MOSFETの耐久性が大きな関心事となります。過電流状態では、SiC MOSFETは、短絡応答保護回路が作動してゲート制御信号がデバイスをシャットダウンするまで、十分に長い時間、大電流と高いDCバス電圧を同時に処理しなければなりません。

臨界エネルギー(Ec)は、パワーデバイスのロバスト性の重要な指標であり、1回の短絡イベント後に試験デバイスの故障につながる最小の散逸エネルギー量を指す。

デバイス・メーカーは通常、短絡耐量を規定しており、これはデバイスが損傷を受ける前に短絡事象を処理できる時間である。

短絡電流は、Vds/Rdsonとデバイス飽和電流のいずれか小さい方によって制限される。

報告されている文献によると、1200VのSiC MOSFETは、室温で600Vdcのバス電圧と20Vのゲート駆動の下で、5~14μsの短絡に耐えることができるが、これはSi IGBTの同等品よりもかなり悪い。

SiCやGaNデバイスはダイが小さいため、電流密度が高くなると、標準的なSiデバイスに比べて温度上昇が速くなり、故障までの時間が短くなり、保護時間を短縮する必要がある。

図5は、同じ電圧・電流定格の2つの異なるスイッチング・デバイスの短絡動作を比較したものである。IGBT(紫色の曲線)の短絡耐時間は約38マイクロ秒であるのに対し、同等のSiCデバイス(赤色の曲線)は8マイクロ秒である。IGBTのピーク短絡電流は最大200アンペアであるのに対し、SiCデバイスはほぼ2倍である。

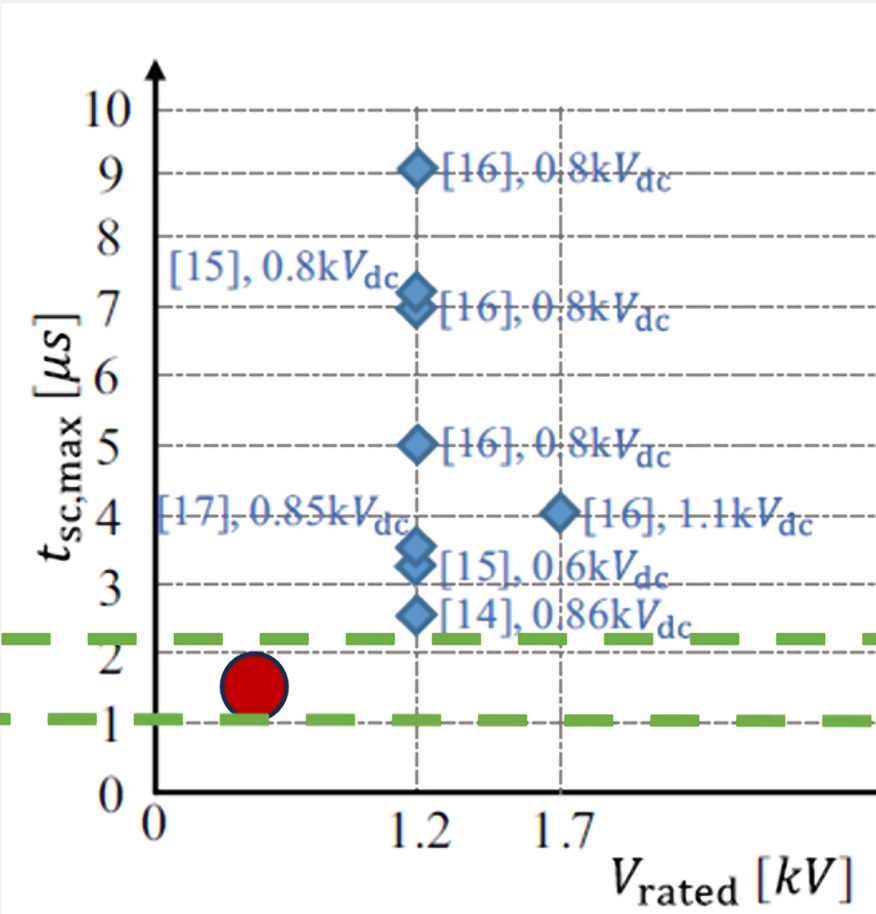

ドライバに実装される短絡保護は、SiC デバイスの最大短絡耐量よりもかなり速い応答時間を持つ必要があります。以下の図6は、SiCモジュールの定格ドレイン・ソース間電圧の関数としての最大短絡応答時間を、指示された試験中のDCリンク電圧でまとめたものである。2μs以下の短絡応答時間は、1回の短絡に対して比較的安全である。一般に、短絡耐量時間は、デバイス面積とMOSFETチャネル長が大きいほど長くなります6。

短絡応答時間が短いほど、デバイスは複数の短絡事象に耐えることができる。しかし、短絡耐性時間には普遍的な固定値はなく、電圧バス、パッケージ-ダイ特性、ダイ面積などの要因によって変化する。例えば、TO-247パッケージのSiC MOSFETの短絡耐量は、800Vで1.7μs、400Vで約10μsである。

図7は、DCバス電圧に対するさまざまなタイプのパワートランジスタの故障時間をまとめたものである。EモードGaN HEMTの故障時間は、SiおよびSiC MOSFETの故障時間よりもはるかに短いことに注意してください。

400Vの直流電圧バスで動作する650VのGaNの短絡耐量の測定値は約630nsecであった。

短絡耐量は、臨界エネルギー(Ec)を用いて計算することができる:

図5: 1200 V/40 A SiC MOSFET と 1200 V/40 A Si IGBT のVds= 600 V、Tc = 25°C における短絡電流比較4

図6:SiCモジュールの短絡応答時間(SCRT)

図7:異なるタイプのパワー・トランジスタの故障時間

典型的なSiC MOSFETの短絡動作

図 8 は、低インダクタンス非破壊試験の典型的な短絡波形を示している。DC バスを 400 Vdc に制限したプレーナー SiC 1200 V で、デバイスの生存を保証するため、2.2 μs の短絡パルスを使用した低インダクタンス(60 nH)短絡試験を実施する。波形は4つのフェーズで見ることができる:

- フェーズA:SiC MOSFETがカットオフ領域からオーミック領域に遷移。ループインダクタンスが小さいため、電流が急激に上昇し始める。この場合、di/dtは約4A/nsであり、1μs以内に最大1kAの電流が流れる。1.1μsでフェーズAが終了すると、短絡エネルギーは約0.4Jとなり、デバイスの最大散逸限界を超える。従って、デバイスが飽和領域に入る前に、短絡回路

保護を作動させる必要がある。 - フェーズB:SiC MOSFETが飽和領域に入り、短絡エネルギーが増加し続ける。

- フェーズC:SiC MOSFETは飽和領域にとどまる。Rds,onの増加により、Idはピークから低下する。

- フェーズD:SiC MOSFETがオフになると(保護機能が作動すると)、高いdI/dt(33A/ns)により、ピーク

、2.2kVの電圧オーバーシュートが発生する。

短絡保護は、緑色(線形)領域内、通常1~2μsの時間枠内で作動すべきである。短絡が検出されると、オーバーシュートを最小限に抑えるために、制御されたスルーレート(ソフトスイッチ機能)で MOSFET をオフにする必要があります。

以下の図9は、700V Microchip社製プレーナ型SiC MOSFETの耐圧時間を、ゲート-ソース間電圧とDC電圧バスの関数として示しています。予想通り、Vgsを下げると耐圧時間は長くなります。これにより、短絡検出後のSiC MOSFETのターンオフをより適切に制御し、オーバーシュート(ソフトターンオフ)を最小限に抑えることができます。マイクロチップのプレーナ型SiC MOSFETの優れた耐圧時間が高く評価されている注目すべきアプリケーションの1つは、ソリッド・ステート・サーキット・ブレーカ(SSCB)またはEヒューズです8。

図8: 典型的なSiC MOSFETの短絡動作7

図9:Microchip SiC MOSFETの短絡耐量は、DCリンク電圧と印加Vgsに依存し、3μsから14μsである。

DESAT保護回路9

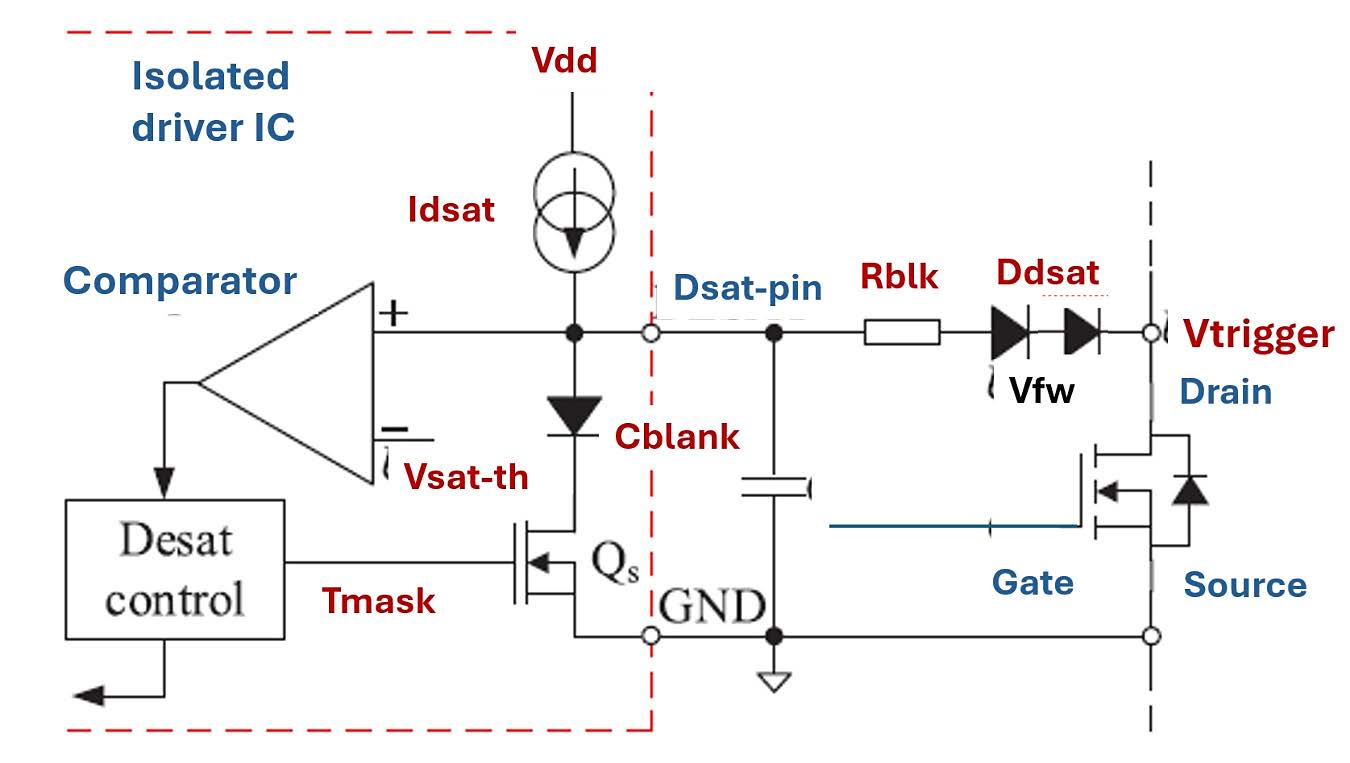

デサチュレーション(DESAT)回路は、IGBT回路の過電流および短絡保護に広く使用されている方法です。この回路は、デバイスが完全にオンしているときにドレイン・ソース間電圧を監視し、短絡または過電流が検出された場合に自動的にシャットオフすることで動作します。

もともとIGBT用に設計されたDESAT回路内蔵の絶縁ゲート・ドライバは、SiC MOSFETやGaNデバイスにも使用できる。

通常、図10に示すように、DESAT回路はゲート・ドライバに統合されており、必要な外付け部品は高速高電圧ダイオード(Ddsat)または直列の複数のダイオード、ブランキング・キャパシタ(Cblank)、抵抗(Rblk)のみである。

MOSFETがオンになると、電流源(Idsat)がコンデンサを充電し、スイッチング中の誤トリガを防止するためのブランキング期間が形成される。コンデンサ電圧がMOSFETのドレイン・ソース間電圧と一致すると、ダイオードは順方向バイアスになる。MOSFETのドレイン・ソース間電圧(Vds)が保護しきい値(Vth-dsat)に達し、ダイオードの順方向電圧降下と直列抵抗にかかる電圧(Idsat×Rdsat)が差し引かれると、短絡がトリガされる。

図10:IGBTやSiC MOSFETのゲート・ドライバで一般的に使用される、過電流や短絡状態から保護するための典型的なDESAT保護回路

抵抗値を調整したり、複数のダイオードを直列に使用することで、トリガー電圧を変更することができる。

通常、DESAT のトリガーポイントは最大ピーク電流の 2 倍に設定されるが、短絡時の最大希望電流に注意深く調整する必要がある。

DESATダイオードは、急激な電圧変化(dv/dt)に起因するノイズの影響を最小限に抑えるため、接合容量が小さい高速回復型でなければならない。

ブランキング時間は、MOSFET のターンオン段階での誤トリガを防止し、ターンオン発振が落ち着くように設定される。トリガー電圧(Vtrigger)とブランキング時間は、SiC MOSFETの特性やターンオンの挙動に基づいて微調整する必要があります。

短絡時の総エネルギーが、SiCメーカーが指定する最大耐量の4分の1以下になるようにすることが重要である。

DESAT 回路はシンプルで実装が容易であり、電力損失も最小である。しかし、SiC MOSFET を使用する場合には、ある課題がある。順方向ダイオードは高電圧に耐え、素早く応答する必要があり、固定ブランキング時間は短絡

保護応答を遅らせる可能性がある。

DESAT 法は、すべての故障状態において一貫した精度を提供するとは限らないことに注意することが重要である。ハードスイッチング故障や負荷下の故障のような異なる故障シナリオでは、応答時間が変化する可能性があります。それにもかかわらず、主な目的は、低インダクタンスで急激な電流サージが存在する場合でも、デバイスの致命的な故障を防止することです。

例えば、典型的なSiCモジュールを保護する場合、DESATしきい値電圧のわずか0.5Vの変動は、ドレイン電流の最大100Aの差に対応する。

SiC MOSFETの故障応答時間

短絡応答時間(SCRT)は、SiC MOSFETでは1μsに制限されるべきである。図11に示すように、保護応答時間の合計は4つの要素の合計である:

- t_mask:SiC MOSFET の初回ターンオン時の電圧スパイクによる保護回路の誤トリガを防止するため、DESAT ピンを意図的に Low に保持(グランドに接続)する固定時間。この時間は通常200~300nsに設定される。

- t_blank:C_blankコンデンサを内部電流源または外部抵抗で充電する時間。

- t_filter:DESAT電圧がしきい値に達してからMOSFETのゲートにターンオフ・コマンドが発行されるまでの標準的な内部遅延。

- t_soft:SiC MOSFETのターンオフ過程における過電圧スパイクのリスクを低減するために追加されるソフト・シャットダウン時間。

下の図 12 に示す波形は、MOSFET が故障状態でオンするハードスイッチ故障のシナリオ中にベンチでキャプチャされたものである。この場合、ブランキング時間がフォルト検出の総時間となり、その後、一般的に外部コンデンサを充電するプルアップ抵抗によって定義されるランプ時間が続く。このランプは、電圧がスレッショルドに達するまで続き、ソフトシャットダウンシーケンスがトリガーされる。

一番下の黄色のトレースは、ゲート・ソース間電圧が上昇していることを示しており、短絡保護が作動するとソフト・シャットダウン・モードに移行する。

前述したように、DESAT 回路の総反応は 1-2usec 以内であるべきである。Dsatピンのノイズ耐性を損なうことなく検出時間を高速化するために、

外部電流源を追加することでCblankコンデンサの内部充電電流を増加させることが可能である。良好なノイズ耐性を維持するために、Cblankコンデンサは300pF以上の値を持つべきである。

図 13 は、Cblank コンデンサの容量値を下げることなく、より高速な充電時間を得るために使用できる外 部回路構成を示している。このソリューションは、カスコード GaN デバイスにも実装でき、400 ns を下回る総応答時間を実現することができる12。

以下の図 14 は、GaN HEMT デバイス用に特別に設計されテストされた、高速検出と保護に最適化されたディスク リート短絡保護回路を示しています。この回路は、総応答時間 122 ns でテストされています13。

基本原理は、オン状態のデバイスを横切る Vds-on(Vsense)を測定し、基準電圧と比較することである。Vsense が Vref を超えると、コンパレータはハイ・フォルト信号(FLT)を供給する。ターンオフ信号はVsense電圧をリセットするために使用される。

絶縁ドライバを使用する場合、FLT 信号をアイソレータを介してドライバに送り返すことができる。ドライバへの FLT 信号は、ゲート・ドライバをディセーブルにし、GaN デバイスを強制的にターンオフさせることができる。超高速応答時間を達成するためには、伝搬遅延の短い絶縁ドライバが望ましい。

図11:プロテクションの総レスポンスタイム

図12:アナログ・デバイセズの絶縁ゲート・ドライバを搭載したSiCモジュールのハードスイッチ故障シナリオ11。

図13:容量値を下げることなく、Cblankコンデンサの充電時間を短縮するための外部回路構成

図 14:GaN HEMT デバイスの超高速応答時間13

ゲート電流要件と電力損失

所望のスイッチング速度を達成するためには、適切な駆動電流容量を持つゲート・ドライバを選択することが不可欠である。

ピーク・ソース電流とピーク・シンク電流は、ゲート-ソース端子間に印加される電圧(dVgdr)を抵抗経路の合計で割ることで簡単に計算できる:

RginはSiC MOSFETの内部ゲート抵抗を表し、Rgonextと Rgoffextはターンオンとターンオフの速度を制御するために使用される外部ゲート抵抗である。同様に、Rgondriverと Rgoffdriverはゲート・ドライバの内部抵抗を示します。

外付け抵抗がスイッチング速度を効果的に調整できるように、ソース電流とシンク電流はドライバのピーク電流制限内に収まるようにする。

高周波または大電流のSiCアプリケーションで放熱を改善し、ゲートピーク電流を高めるには、外付けトーテムポールバイポーラトランジスタを推奨する。

図15に、Skyworks製Si828x絶縁型ドライバの基本的なドライブ強化回路を示します。バイポーラトランジスタQ1とQ2は、VHとVL信号によって制御され、ドライバ電流を調整します。右の画像は、ゲート容量220 pFで最大30 Aのピークソース電流を示しています。

特に大型モジュール・アプリケーションでは、外付けトーテムポール回路により、トランジスタをMOSFETゲートの近くに配置できるため、レイアウトと性能の最適化に役立ちます。これにより、ゲート回路のインダクタンスが最小化され、デバイスのゲート・ピンでの電位リンギングが減少します。さらに、この外付け回路は、ドライバの最大消費電力能力を超えることを防ぎます。

ゲート回路に必要な総電力は、SiC MOSFETの総ゲート電荷量(Qg)に、ゲート-ソース端子間に印加される電圧(dVgdr)とスイッチング周波数(fsw)を乗算することで求められる:

結論

全体として、絶縁ゲート・ドライバ技術の継続的な進歩は、WBGデバイスを様々なアプリケーションにうまく統合し、より効率的で信頼性の高いパワー・エレクトロニクス・システムへの道を開くために不可欠である。

参考文献

(*1) AN583 デジタル・アイソレータの安全配慮とレイアウト推奨 - Skyworks

(*2) ND90204 EliteSiC Gen 2 1200V MOFET アプリケーションノート - ONSEMI

(*3) 絶縁ゲートドライバのピーク電流 - Analog Devices

(*4) SIC MOSFET のラグドネスと信頼性のレビューと解析 - Jun Wang、Xi Jiang - Feb 2020

(*5) AN5355 ミラークランプによるSIC MOSFETゲート電圧グリッチの緩和技術

(*6) SiC MOSFETモジュールの短絡保護に関する比較と考察, Slavko Mocevic IEEE

(*7) 出典:短絡動作におけるSiC MOSFETのロバスト性に関する新しい臨界エネルギーの定義。

(*8) EV アプリケーション向け SiC ベース補助 E ヒューズ技術デモ - Microchip - PCIM Europe

(*9) AN1288:Si828x External Enhancement Circuit - Skyworks SiC パワーモジュールの改良型脱飽和短絡保護方式 サイエンス・ダイレクト

(*10) SiC パワーモジュールの改良型脱飽和短絡保護方式 サイエンス・ダイレクト (CPESE 2021)

(*11) Wolfspeed- Analog Device - Isolated Gate driver seminar

(*12) AN1288:Si828x External Enhancement Circuit- Skyworks

(*13) A Simple Desaturation Based Protection Circuit for GaN HEMT With Ultrafast response time - IEEE June 2021

(*14) AN1288 Si828x External Enhancement Cicuit - Skyworks DN80 - MOSFETゲート駆動用バイポーラトランジスタ - Diodes