I dispositivi a banda larga (WBG), come il carburo di silicio (SiC) e il nitruro di gallio (GaN), presentano analogie operative con i MOSFET e gli IGBT a base di silicio, ma caratteristiche elettriche distinte che richiedono soluzioni di pilotaggio del gate specializzate. Questo articolo esplora i requisiti chiave per la progettazione di gate driver isolati ottimizzati per i dispositivi WBG, evidenziando i progressi critici che migliorano le prestazioni, l'efficienza e l'affidabilità.

autore

Michele Sclocchi

Ingegnere applicativo energia e potenza

Sud Europa e Israele

Requisito di isolamento

I dispositivi SiC sono progettati per funzionare a tensioni elevate per periodi prolungati. Un gate driver isolato garantisce che il circuito di controllo sia protetto da queste tensioni elevate, migliorando l'affidabilità e la sicurezza del sistema.

Ogni componente di sicurezza ha un profilo di rottura dielettrica dipendente dal tempo. I produttori di componenti isolati di solito forniscono standard di certificazione e dati sul profilo di isolamento.

La tensione di isolamento (VISO) è definita dalla massima tensione di resistenza con durata di un minuto, con un valore tipico di 5,0 kVrms/1 min.

L'isolamento massimo di lavoro (VIOWM) è la tensione massima di isolamento che il dispositivo può utilizzare in modo continuo, di solito con una durata prevista superiore a 23 anni.

La Figura 1, qui di seguito, mostra la durata della tensione del prodotto isolato con 5 kVrms di Skyworks a diverse tensioni di esercizio; a 1 kVrms, la durata prevista è di 100 anni.1

Il massimo grado di isolamento delle sovratensioni (VIOSM) ha lo scopo di simulare la condizione di fulmine. Si tratta del test di isolamento ad alta tensione più severo, in cui una forma d'onda di sovratensione predefinita da 10 kV viene applicata direttamente al componente.

Gli standard industriali specificano anche i requisiti di distanza minima tra i contatti metallici esterni ai dispositivi di isolamento. Lo spazio libero è la distanza misurata lungo la superficie e la distanza minima tra due conduttori.

Le distanze minime di dispersione e di passaggio sono definite dagli organismi normativi IEC a titolo indicativo, al fine di evitare la formazione di archi elettrici durante il funzionamento. Essi dipendono dalla tensione di esercizio, dal gruppo di materiali, dalla classe e dalla tecnologia, dalla considerazione dell'ambiente, dall'altitudine e dall'inquinamento e dall'uso dell'apparecchiatura.

Alcune applicazioni richiedono anche isolamenti rinforzati, ottenuti utilizzando due livelli di isolamento in serie. Ciò significa che se uno strato si guasta, il secondo strato continua a fornire una protezione di sicurezza. Gli isolatori rinforzati sono dispositivi che forniscono un isolamento equivalente a due isolatori di base in serie.

La tabella 1 riassume le specifiche di tensione di isolamento dei driver isolati tipicamente suggeriti per le applicazioni SiC e GaN.

Figura 1: isolatore digitale Si86xxxD di Skyworks con ripartizione dielettrica in funzione del tempo

I continui progressi nella tecnologia dei driver per gate isolati sono essenziali per il successo dell'integrazione dei dispositivi WBG, aprendo la strada a sistemi di elettronica di potenza più efficienti e affidabili.

Produttore | Numero di parte | Valutazione dell'isolamento | Tensione di lavoro | Isolamento rinforzato | Minima distanza tra i due lati | Tensione di uscita massima |

|---|---|---|---|---|---|---|

V rms | V (picco) | V (picco) | mm | V | ||

ADI | ADuM4146 | 5000 | 2150 | 8 | 30 | |

ADI | ADuM4121 | 5000 | 849 | 558 | 8 | 35 |

Skyworks | Si8281/2/3/4 | 5000 | 1400 | 840 | 8 | 30 |

Skyworks | Si8285 | 5000 | 1400 | 840 | 8 | 30 |

onsemi | NCD57084 | 2500 | 1200 | P | 8 | 36 |

onsemi | NCD57100 | 5000 | 1000 | P | 8 | 36 |

onsemi | NCP51752 | 3500 | 870 | P | 4 | 33 |

Skyworks | Si827x | 2500 | 849 | 155 | 3.9 | 30 |

Skyworks | Si82Fx | 6000 | 1860 | 849 | 8 | 30 |

ADI | MAX2270x | 5000 | 1000 | 8 | 28 |

Tabella 1: Specifiche tipiche della tensione di isolamento dei driver isolati per applicazioni SiC e GaN

Requisiti di tensione di pilotaggio2

La transconduttanza di un MOSFET è un parametro importante per determinare i tempi di commutazione, in quanto influenza la tensione di plateau Miller gate-source durante la commutazione.

La transconduttanza (gfs) è definita come il rapporto tra la variazione della corrente di drenaggio e la variazione della tensione di gate. I MOSFET in carburo di silicio hanno una transconduttanza relativamente più bassa rispetto ai MOSFET in silicio (in genere 2,6 S contro 15-20 S, rispettivamente). Per compensare questa transconduttanza inferiore e ottenere un'ampia variazione della corrente di drenaggio, si applica una tensione gate-source più elevata.

Inoltre, i MOSFET SiC tendono a rimanere nella regione ohmica in un intervallo di Vgs più ampio, quindi è importante avere una transizione rapida per ridurre al minimo le perdite.

I MOSFET SiC disponibili sul mercato sono classificati in base alla loro tensione di soglia (VTH). I MOSFET SiC ad alta soglia hanno valori tipici superiori a 3,5 V; i MOSFET SiC a bassa soglia hanno valori tipici che vanno da 3 V a 3,5 V. La tensione di soglia può variare in base alla temperatura, scendendo fino a 1,8 V o salendo fino a 4,3 V.

Nelle configurazioni double-ended (MOSFET high-side e low-side), dove può verificarsi il fenomeno dello shoot-through, si raccomanda una polarizzazione negativa del gate per fornire un margine di sicurezza sufficiente e prevenire l'accensione parassita, soprattutto ad alte frequenze di commutazione.

La tensione di pilotaggio del gate operativo viene determinata valutando fattori di prestazione quali le perdite di conduzione (Rdson) e le perdite di commutazione nell'ambito dei valori raccomandati per la tensione del gate SiC.

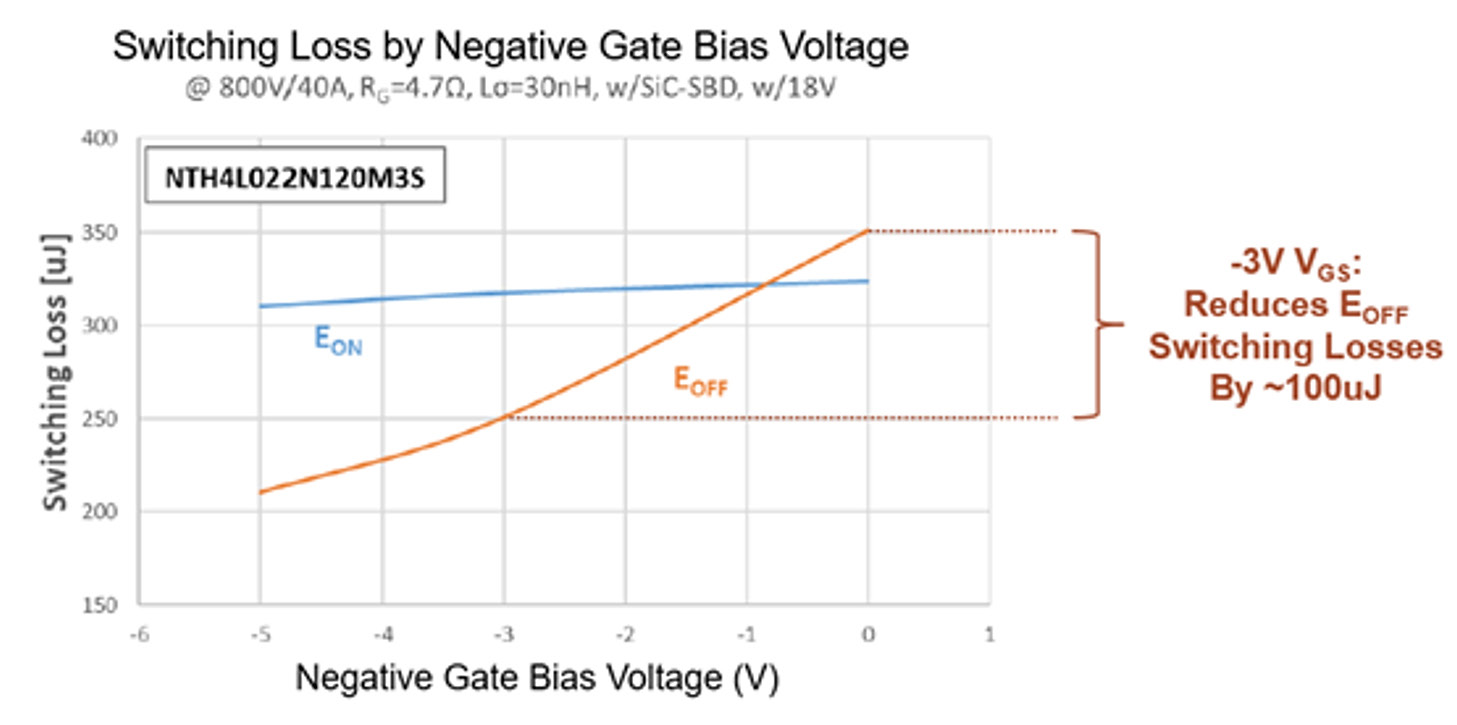

La Figura 2 mostra la tensione di spegnimento in polarizzazione negativa da 0 V a -5 V (asse x) e le perdite di commutazione (uJ) (asse y). Si noti che il pilotaggio del turnoff con -3 V riduce le perdite di spegnimento (Eoff) del 25%.

Figura 2: Perdita di commutazione ONSEMI SiC in funzione della tensione negativa di polarizzazione del gate (sorgente ONSEMI ND90204/D)

Blocco per sottotensione (UVLO)

L'undervoltage-lockout è una funzione progettata per proteggere i sistemi in caso di guasto dell'alimentazione di polarizzazione. Il circuito UVLO monitora continuamente la tensione di alimentazione del gate e disabilita il gate se la tensione scende al di sotto di una soglia definita.

I driver al carburo di silicio richiedono in genere una soglia UVLO più elevata rispetto ai dispositivi al silicio. I driver per gate SiC dedicati spesso includono livelli UVLO programmabili o opzioni predefinite, con soglie che vanno da 10 V a 16 V. L'UVLO deve essere impostato significativamente al di sopra della regione di plateau di Miller (8-9 V) e allineato con le capacità termiche del dispositivo SiC.

La Figura 3 illustra le tipiche caratteristiche on-state di un MOSFET SiC a vari livelli di tensione gate-to-source (Vgs). Se il sistema funziona a 150 A con una tensione nominale di gate di 20 V e l'UVLO è impostato a 15 V, la caduta di tensione drain-source (Vds) si riduce a una frazione minima di volt (dal punto A al punto B).

Tuttavia, se l'UVLO è impostato al di sotto di 12 V, la protezione termica diventa inadeguata, provocando una caduta di tensione più che doppia rispetto al livello previsto (punto C).

Figura 3: Tensione di caduta on-state di un dispositivo MOSFET SiC a diversi livelli di tensione di gate

Corrente di picco del driver3

La corrente di picco è spesso evidenziata nelle schede tecniche dei driver per gate, ma la sua definizione può variare da un produttore all'altro. In genere, le schede tecniche definiscono la corrente di picco come la corrente di saturazione, misurata mettendo in cortocircuito l'uscita con una grande capacità o pulsando brevemente il driver in un cortocircuito. Tuttavia, raramente sono incluse curve I-V dettagliate che mostrano i valori minimi e massimi a diverse temperature e variazioni di produzione.

Una definizione alternativa di corrente di picco prevede di specificare la corrente massima all'interno della regione lineare della curva I-V più bassa. Questo approccio conservativo garantisce che i FET di uscita del gate driver non vadano in saturazione in tutte le condizioni di temperatura e di processo, a condizione che la resistenza di gate esterna sia dimensionata correttamente.

Oltre al valore della corrente di picco, è importante considerare specifiche come la resistenza di sink e source degli interruttori interni e i tempi di salita e discesa in condizioni specifiche. Ad esempio, la resistenza degli interruttori interni di pull-up e pull-down influisce in modo significativo sulla corrente media e sulla dissipazione di potenza nel driver e nella resistenza di gate esterna.

La Tabella 2 riassume la tensione, la corrente e la velocità di vari gate driver isolati, evidenziando le opzioni adatte alle tipiche applicazioni SiC.

Produttore | Numero di parte | Tensione di uscita massima | Picco I out (Source/Sink) | Resistenza Rout (Source/Sink) | Tempo di salita/discesa dell'uscita | Ritardo di propagazione (ns) |

|---|---|---|---|---|---|---|

V | A | Ω | nS | nsec | ||

ADI | ADuM4146 | 30 | 11 | 0.6 | 18 | 44 |

ADI | ADuM4121 | 35 | 2 | 1.8/1.6 | 18 | 53 |

Skyworks | Si8281/2/3/4 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 50 |

Skyworks | Si8285 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 40 |

onsemi | NCD57084 | 36 | 7 | 10 | 60 | |

onsemi | NCD57100 | 36 | 7 | 15 | 70 | |

onsemi | NCP51752 | 33 | 4.5/9 | 1.4/0.5 | 15/8 | 36 |

Skyworks | Si827x | 30 | 1.8/4.0 | 2.7/1.0 | 10/13 | 45 |

Skyworks | Si82Fx | 30 | 4 | 0.7 | 15 | 30 |

ADI | MAX2270x | 28 | 4/5.7 | 1.25 | 3.6/2.5 | 5 |

Immunità ai transitori di modo comune (CMTI) e capacità di isolamento4

L'immunità ai transitori di modo comune (CMTI) è un fattore chiave nella scelta dei driver per gate isolati. Il CMTI si riferisce alla massima velocità di variazione ammissibile della tensione di modo comune tra due circuiti isolati. In genere, il rating CMTI per un gate driver isolato dovrebbe superare la velocità di commutazione massima dei dispositivi SiC. Con una velocità di commutazione tipica di 50 V/nS, il valore CMTI dovrebbe essere superiore a 100 V/ns. Molte delle ultime generazioni di driver isolati SiC e GaN hanno valori CMTI superiori a 200 kV/uS.

I dispositivi a commutazione rapida come SiC e GaN con gate driver a basso CMTI possono presentare diversi problemi, come guasti, impulsi mancati, aumento del ritardo di propagazione e prolungamento del tempo morto.

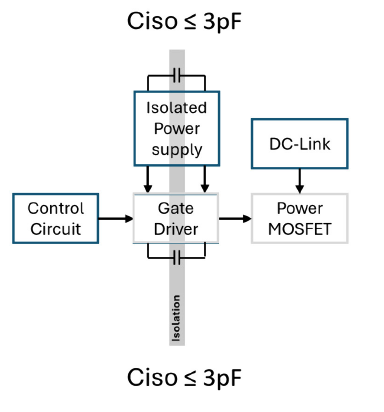

Un altro fattore importante da considerare è la capacità parassita di isolamento (Ciso), solitamente misurata in pochi picofarad tra il pin di controllo di ingresso e l'uscita. In un'applicazione SiC con una velocità di transizione rapida di 100 V/ns e 2 pF di capacità di isolamento, ciò può comportare un flusso di corrente di 200 mA attraverso il confine di isolamento.

Tabella 3: Riepilogo delle capacità tipiche di CMTI e di isolamento dei driver isolati per dispositivi SiC e GaN

Questa considerazione vale anche per i convertitori CC-CC isolati utilizzati per fornire le tensioni di gate positive e negative al dispositivo. È importante scegliere convertitori progettati per applicazioni SiC e GaN con una capacità di isolamento molto bassa tra primario e secondario. Ad esempio, la nuova famiglia di convertitori DC-DC isolati di RECOM (R12C2T25/R) presenta una capacità di isolamento inferiore a 3,5 pF.

Morsetto attivo Miller

Gli eventi di cortocircuito possono verificarsi nell'azionamento dei motori e in altri sistemi di elettronica di potenza, rendendo la robustezza dei MOSFET SiC una delle principali preoccupazioni in queste applicazioni. In condizioni di sovracorrente, i MOSFET SiC devono gestire simultaneamente grandi correnti ed elevate tensioni del bus DC per un tempo sufficientemente lungo, fino a quando i circuiti di protezione dalla risposta al cortocircuito si attivano e il segnale di controllo del gate spegne il dispositivo.

L'energia critica (Ec), una metrica essenziale di robustezza per i dispositivi di potenza, si riferisce alla quantità minima di energia dissipata che porta al guasto del dispositivo testato dopo un singolo evento di cortocircuito.

I produttori di dispositivi specificano in genere una capacità di resistenza al cortocircuito, ovvero la quantità di tempo in cui un dispositivo può gestire un evento di cortocircuito prima di subire danni.

La corrente di cortocircuito è limitata da Vds/Rdson e dalla corrente di saturazione del dispositivo, a seconda di quale sia più piccola.

Secondo la letteratura riportata, un MOSFET SiC da 1200 V può resistere a un evento di cortocircuito per 5-14 μs con una tensione di bus di 600 Vdc e un gate drive di 20 V a temperatura ambiente, il che è significativamente peggiore delle controparti IGBT Si.

Poiché i dispositivi SiC e GaN hanno matrici di dimensioni ridotte, la maggiore densità di corrente provoca un aumento di temperatura più rapido rispetto ai dispositivi Si standard, che si traduce in un time-to-failure più breve e richiede tempi di protezione più rapidi.

La Figura 5 confronta il comportamento in cortocircuito di due diversi dispositivi di commutazione con la stessa tensione e corrente nominale. Il tempo di resistenza al cortocircuito dell'IGBT (curva viola) è di circa 38 microsecondi rispetto agli 8 microsecondi del dispositivo SiC equivalente (curva rossa). La corrente di picco di cortocircuito dell'IGBT raggiunge i 200 ampere, mentre è quasi doppia per il dispositivo SiC.

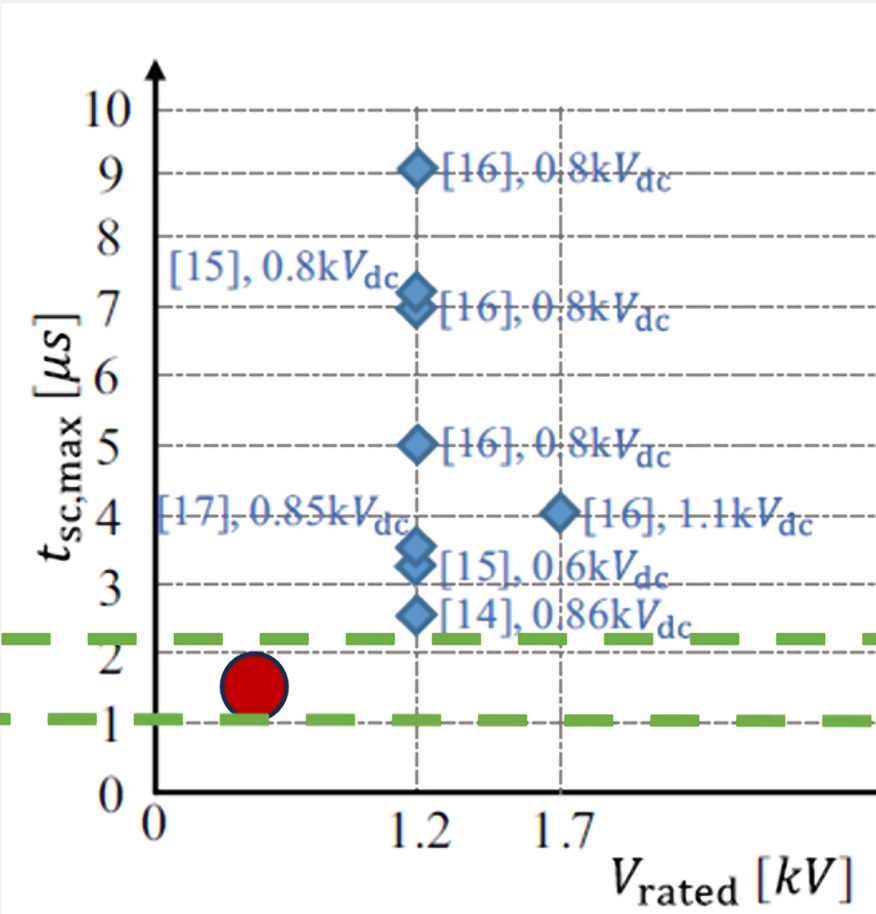

La protezione da cortocircuito implementata nel driver deve avere un tempo di risposta significativamente più veloce del tempo massimo di resistenza al cortocircuito del dispositivo SiC. La Figura 6, qui di seguito, riassume il tempo massimo di risposta al cortocircuito dei moduli SiC in funzione della tensione nominale drain-to-source con la tensione del circuito intermedio indicata nel test. Un tempo di risposta al cortocircuito inferiore a 2 μs è relativamente sicuro per un singolo evento di cortocircuito. In generale, il tempo di resistenza al cortocircuito aumenta con l'aumentare dell'area del dispositivo e della lunghezza del canale del MOSFET.6

Più breve è il tempo di risposta al cortocircuito, maggiore è la capacità del dispositivo di resistere a più eventi di cortocircuito. Tuttavia, non esiste un valore universalmente fisso per il tempo di resistenza al cortocircuito; esso varia in base a fattori quali il bus di tensione, le caratteristiche del package e l'area del die. Ad esempio, un MOSFET SiC in un contenitore TO-247 ha un tempo di resistenza al cortocircuito di 1,7 μs a 800 V e di circa 10 μs a 400 V.

La Figura 7 riassume i tempi di guasto dei diversi tipi di transistor di potenza in funzione della tensione del bus CC. Si noti che i tempi di guasto del GaN HEMT in modalità E sono molto inferiori a quelli dei MOSFET Si e SiC.

Il tempo di resistenza al cortocircuito misurato di un GaN da 650 V, funzionante con un bus di tensione CC di 400 V, è di circa 630 nsec.

Il tempo di resistenza al cortocircuito può essere calcolato utilizzando l'energia critica (Ec):

Figura 5: Confronto della corrente di cortocircuito del MOSFET SiC da 1200 V/40 A e dell'IGBT Si da 1200 V/40 A sotto Vds = 600 V e Tc = 25°C4

Figura 6: Tempo di risposta ai cortocircuiti (SCRT) dei moduli SiC

Figura 7: Tempo di guasto di diversi tipi di transistor di potenza

Comportamento tipico del MOSFET SiC in cortocircuito

La Figura 8 mostra le tipiche forme d'onda di cortocircuito di un test non distruttivo a bassa induttanza. Un SiC 1200 V planare, con un bus CC limitato a 400 V CC, viene sottoposto a un test di cortocircuito a bassa induttanza (60 nH) utilizzando un impulso di cortocircuito di 2,2 μs per garantire la sopravvivenza del dispositivo. Le forme d'onda possono essere visualizzate in quattro fasi:

- Fase A: il MOSFET SiC passa dalla regione di cutoff alla regione ohmica. La corrente inizia a salire rapidamente a causa della piccola induttanza del loop. In questo caso, il di/dt è di circa 4 A/ns, con una corrente fino a 1 kA entro 1 μs. A 1,1 μs, al termine della fase A, l'energia di cortocircuito è di circa 0,4 J, che supera il limite massimo di dissipazione del dispositivo. Pertanto, la protezione da cortocircuito

deve essere attivata prima che il dispositivo entri nella regione di saturazione. - Fase B: il MOSFET SiC entra nella regione di saturazione e l'energia di cortocircuito continua ad aumentare.

- Fase C: il MOSFET SiC rimane nella regione di saturazione. L'aumento di Rds,on determina una diminuzione di Id dal suo picco.

- Fase D: Quando il MOSFET SiC è spento (quando la protezione è attivata), l'elevato dI/dt (33 A/ns) induce un picco di sovratensione

di 2,2 kV.

La protezione da cortocircuito deve essere attivata entro la regione verde (lineare), in genere entro un intervallo di tempo di 1-2 μs. Quando viene rilevato il cortocircuito, il MOSFET deve essere spento con una velocità di rotazione controllata (funzione soft-switch) per ridurre al minimo gli overshoots.

La Figura 9 illustra il tempo di resistenza dei MOSFET SiC planari Microchip da 700 V in funzione della tensione gate-to-source e del bus di tensione CC. Come previsto, il tempo di resistenza aumenta quando si riduce la Vgs. Ciò consente di controllare meglio lo spegnimento del MOSFET SiC dopo il rilevamento del cortocircuito per ridurre al minimo l'overshoot (soft-turnoff). Un'importante applicazione in cui il tempo di resistenza superiore dei MOSFET SiC planari di Microchip è molto apprezzato è quella degli interruttori automatici a stato solido (SSCB) o dei fusibiliE8.

Figura 8: Comportamento tipico del MOSFET SiC in cortocircuito7

Figura 9: I MOSFET SiC di Microchip presentano tempi di resistenza al cortocircuito compresi tra 3 μs e 14 μs, a seconda della tensione del circuito intermedio e della Vgs applicata.

Circuito di protezione DESAT9

Il circuito di desaturazione (DESAT) è un metodo ampiamente utilizzato per la protezione da sovracorrenti e cortocircuiti nei circuiti IGBT. Funziona monitorando la tensione drain-source quando il dispositivo è completamente acceso e lo spegne automaticamente se viene rilevato un cortocircuito o un evento di sovracorrente.

I gate driver isolati con circuiti DESAT integrati, originariamente progettati per gli IGBT, possono essere utilizzati anche con i MOSFET SiC e i dispositivi GaN.

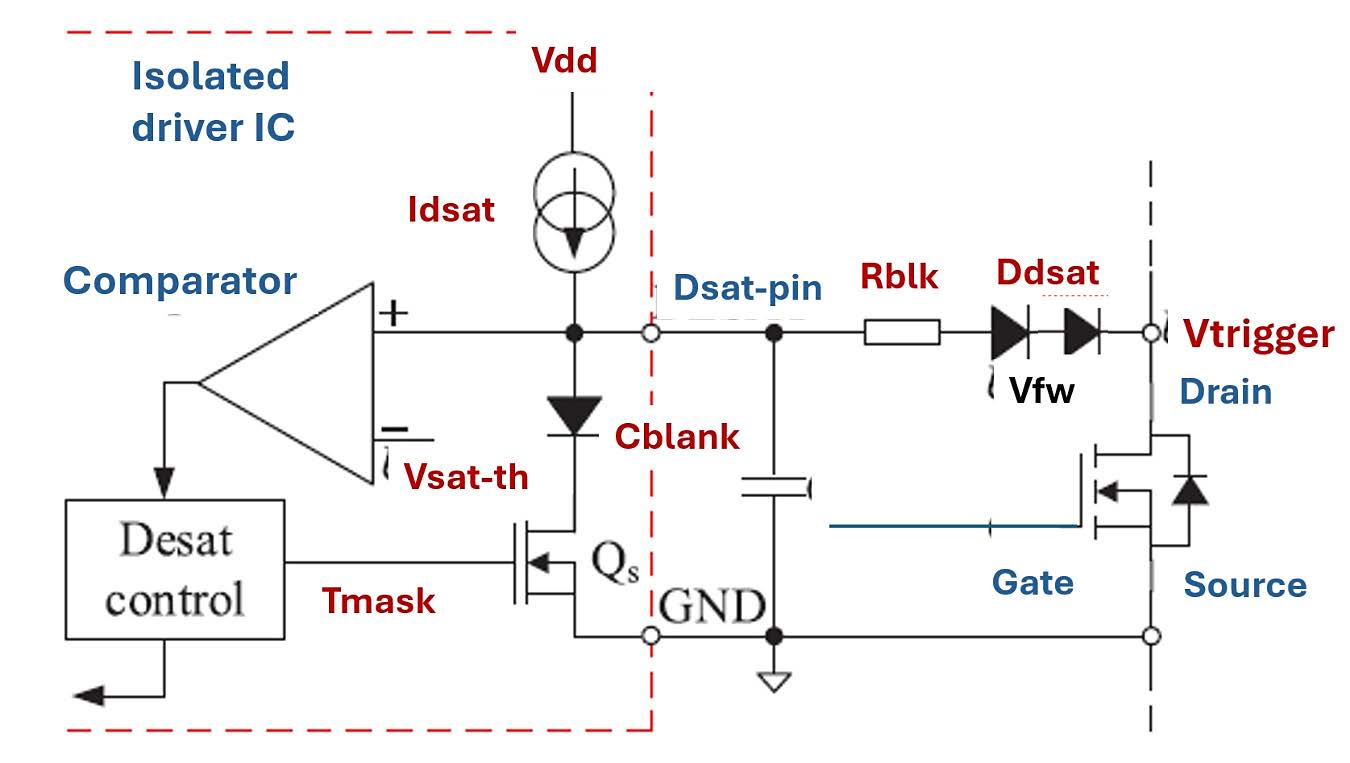

In genere, come mostrato nella Figura 10, il circuito DESAT è integrato nel gate driver e richiede solo pochi componenti esterni: un diodo veloce ad alta tensione (Ddsat) o più diodi in serie, un condensatore di blanking (Cblank) e un resistore (Rblk).

Quando il MOSFET si accende, una sorgente di corrente (Idsat) carica il condensatore, creando un periodo di vuoto per evitare falsi inneschi durante la commutazione. Il diodo diventa in tensione in avanti quando la tensione del condensatore corrisponde alla tensione drain-source del MOSFET. Il cortocircuito si attiva quando la tensione drain-source del MOSFET (Vds) raggiunge la soglia di protezione (Vth-dsat), meno la caduta di tensione in avanti del diodo e la tensione attraverso la resistenza in serie (Idsat × Rdsat).

Figura 10: Tipico circuito di protezione DESAT comunemente utilizzato nei driver di gate per IGBT e MOSFET SiC per proteggere da condizioni di sovracorrente e cortocircuito

La regolazione del valore della resistenza o l'utilizzo di più diodi in serie possono modificare la tensione di attivazione.

In genere, il punto di attivazione DESAT è impostato sul doppio della corrente di picco massima, ma deve essere regolato con attenzione sulla corrente massima desiderata durante un evento di cortocircuito.

Il diodo DESAT deve essere del tipo a recupero rapido con bassa capacità di giunzione per ridurre al minimo la suscettibilità ai disturbi causati da rapide variazioni di tensione (dv/dt).

Il tempo di blanking è configurato per evitare false attivazioni durante la fase di accensione del MOSFET e per consentire alle oscillazioni di accensione di stabilizzarsi. Sia la tensione di attivazione (Vtrigger) che il tempo di blanking devono essere regolati con precisione in base alle caratteristiche specifiche e al comportamento di accensione del MOSFET SiC.

È fondamentale garantire che l'energia totale durante un evento di cortocircuito rimanga al di sotto di un quarto dell'energia massima di resistenza specificata dal produttore di SiC.

Il circuito DESAT è semplice, facile da implementare e ha una perdita di potenza minima. Tuttavia, presenta alcune sfide quando viene utilizzato con i MOSFET SiC. Il diodo forward deve resistere a tensioni elevate e rispondere rapidamente, mentre il tempo di blanking fisso può ritardare la risposta della protezione da cortocircuito

.

È importante notare che il metodo DESAT potrebbe non fornire un'accuratezza costante in tutte le condizioni di guasto. Diversi scenari di guasto, come i guasti con commutazione dura o i guasti sotto carico, possono determinare tempi di risposta variabili. Tuttavia, l'obiettivo primario è quello di prevenire guasti catastrofici del dispositivo, anche in presenza di rapidi picchi di corrente a bassa induttanza.

Per esempio, nella protezione di un tipico modulo SiC, una variazione di soli 0,5 V nella tensione di soglia DESAT può corrispondere a una differenza fino a 100 A nella corrente di drain.

Tempo di risposta ai guasti per i MOSFET SiC

Il tempo di risposta ai cortocircuiti (SCRT) deve essere limitato a 1 μs per i MOSFET SiC. Il tempo di risposta totale della protezione, come illustrato nella Figura 11, è la somma di quattro componenti:

- t_mask: Tempo fisso durante il quale il pin DESAT viene mantenuto intenzionalmente basso (collegato a massa) per evitare un falso innesco del circuito di protezione dovuto a picchi di tensione durante l'accensione iniziale del MOSFET SiC. Questo tempo è tipicamente impostato tra 200-300 ns.

- t_blank: Tempo di carica del condensatore C_blank attraverso la sorgente di corrente interna o un resistore esterno.

- t_filtro: Il tipico ritardo interno tra il raggiungimento della soglia della tensione DESAT e l'emissione del comando di spegnimento al gate del MOSFET.

- t_soft: Tempo di spegnimento morbido, aggiunto per ridurre il rischio di picchi di sovratensione durante il processo di spegnimento del MOSFET SiC.

La forma d'onda mostrata nella Figura 12, qui sotto, è stata catturata su un banco durante uno scenario di guasto hard-switched, in cui il MOSFET si accende in una condizione di guasto. In questo caso, il tempo di blanking aggiunge il tempo totale di rilevamento del guasto, seguito dal tempo di rampa, tipicamente definito da una resistenza di pull-up che carica un condensatore esterno. Questa rampa continua finché la tensione non raggiunge la soglia, innescando la sequenza di spegnimento graduale.

La traccia gialla in basso mostra l'aumento della tensione gate-to-source e, quando la protezione da cortocircuito è attivata, il dispositivo passa in modalità soft shutdown.

Come già detto, la reazione totale del circuito DESAT deve essere compresa entro 1-2 usec.

Per accelerare il tempo di rilevamento senza compromettere l'immunità al rumore del pin Dsat, è possibile aumentare la corrente di carica interna del condensatore Cblank aggiungendo una sorgente di corrente esterna. Per mantenere una buona immunità ai disturbi, il condensatore Cblank deve avere un valore superiore a 300 pF.

La Figura 13 mostra la configurazione del circuito esterno che può essere utilizzata per ottenere un tempo di carica più rapido per il condensatore Cblank, senza ridurre il suo valore di capacità. Questa soluzione può essere implementata anche per i dispositivi GaN in cascata, consentendo un tempo di risposta totale inferiore a 400 ns.12

La Figura 14 mostra un circuito discreto di protezione dai cortocircuiti ottimizzato per il rilevamento e la protezione rapidi, progettato e testato specificamente per i dispositivi GaN HEMT. Questo circuito è stato testato con un tempo di risposta totale di 122 ns.13

Il principio di base consiste nel misurare Vds-on attraverso il dispositivo nello stato di accensione (Vsense) e confrontarlo con una tensione di riferimento. Se Vsense supera Vref, il comparatore fornisce un segnale di errore alto (FLT). Il segnale di spegnimento viene utilizzato per ripristinare la tensione Vsense.

Se si utilizza un driver isolato, il segnale FLT può essere inviato al driver attraverso un isolatore. Il segnale FLT al driver può disabilitare il gate driver, forzando uno spegnimento del dispositivo GaN. I driver isolati con un breve ritardo di propagazione sono preferibili per ottenere tempi di risposta ultrarapidi.

Figura 11: Tempo di risposta della protezione totale

Figura 12: Scenario di guasto dell'interruttore rigido di un modulo SiC con gate driver isolato di Analog Devices.11 Il tempo di risposta totale è mantenuto al di sotto di 1 μs.

Figura 13: Configurazione del circuito esterno per accelerare il tempo di carica del condensatore Cblank, senza ridurre il valore della capacità

Figura 14: Tempo di risposta ultraveloce per dispositivi HEMT GaN13

Requisiti di corrente di gate e dissipazioni di potenza

Per ottenere la velocità di commutazione desiderata, è essenziale scegliere un gate driver con un'adeguata capacità di corrente di pilotaggio.

La corrente di picco di source e sink può essere facilmente calcolata dividendo la tensione applicata al terminale gate-to-source (dVgdr) per la somma delle resistenze del percorso:

Rgin rappresenta la resistenza interna del gate del MOSFET SiC, Rgonext e Rgoffext sono le resistenze esterne del gate utilizzate per controllare le velocità di accensione e spegnimento. Analogamente, Rgondriver e Rgoffdriver indicano la resistenza interna del gate driver.

Per garantire che le resistenze esterne possano regolare efficacemente le velocità di commutazione, la corrente di source e sink deve rimanere entro i limiti di corrente di picco del driver.

Per migliorare la dissipazione del calore e aumentare la corrente di picco del gate nelle applicazioni SiC ad alta frequenza o ad alta corrente, si consiglia di utilizzare un transistor bipolare totem esterno.

La Figura 15 illustra un circuito di potenziamento di base per il driver isolato Si828x di Skyworks. I transistor bipolari Q1 e Q2 regolano la corrente del driver, controllata dai segnali VH e VL. L'immagine a destra illustra una corrente di picco della sorgente fino a 30 A con una capacità di gate di 220 pF.

Soprattutto nelle applicazioni per moduli di grandi dimensioni, il circuito totem esterno contribuisce a ottimizzare il layout e le prestazioni, consentendo di posizionare i transistor più vicini al gate del MOSFET. Questo riduce al minimo l'induttanza del circuito di gate e riduce il potenziale di ringing sul pin di gate del dispositivo. Inoltre, il circuito esterno impedisce di superare la capacità massima di dissipazione di potenza del driver.

La potenza totale richiesta dal circuito di gate è determinata moltiplicando la carica totale del gate (Qg) del MOSFET SiC per la tensione applicata al terminale gate-source (dVgdr) e la frequenza di commutazione (fsw):

Conclusione

Nel complesso, i continui progressi nella tecnologia dei driver per gate isolati sono essenziali per il successo dell'integrazione dei dispositivi WBG in varie applicazioni, aprendo la strada a sistemi elettronici di potenza più efficienti e affidabili.

Riferimenti

(*1) AN583 Safety Considerations and Layout Recommendations for Digital Isolators - Skyworks

(*2) ND90204 EliteSiC Gen 2 1200V MOFETs application note - ONSEMI

(*3) Peak Current of Isolated Gate Driver - Analog Devices

(*4) Revisione e analisi della resistenza e dell'affidabilità dei MOSFET SIC - Jun Wang, Xi Jiang - Feb 2020

(*5) AN5355 Tecniche di mitigazione dei glitch di tensione di gate dei MOSFET SIC con Miller clamp

(*6) Comparison and Discussion on Short-circuit Protection for SiC MOSFET Modules, Slavko Mocevic IEEE

(*7) Source: Nuova definizione di energia critica per la robustezza dei MOSFET SiC nel funzionamento in cortocircuito.

(*8) Dimostratore di tecnologia E-Fuse ausiliaria basata su SiC per applicazioni EV - Microchip - PCIM Europe

(*9) AN1288: Si828x External Enhancement Circuit - Skyworks An improved desaturation short-circuit protection method for SiC power modules science direct

(*10) An improved desaturation short-circuit protection method for SiC power modules science direct (CPESE 2021)

(*11) Wolfspeed- Analog Device - Isolated Gate driver seminar

(*12) AN1288: Si828x External Enhancement Circuit- Skyworks

(*13) Un semplice circuito di protezione basato sulla desaturazione per GaN HEMT con un tempo di risposta ultraveloce - IEEE giugno 2021

(*14) AN1288 Si828x External Enhancement Cicuit - Skyworks DN80 - Transistor bipolari per applicazioni di pilotaggio di gate MOSFET - Diodi