複数のデジタル信号処理(DSP)ブロック、広帯域デジタル・アナログ・コンバーター(DAC)、広帯域アナログ・デジタル・コンバーター(ADC)を単一のモノリシック・チップに統合することで、消費電力の高い FPGA リソースをオフロードできるようになり、フットプリントが小さく、消費電力が低く、チャネル数の多いプラットフォームが実現し、従来よりも高いレートでサンプリングできるようになりました。この新しい機能とともに、これらの集積回路(IC)には新しいマルチチップ同期(MCS)アルゴリズムが搭載されており、ユーザーはシステムの電源投入時や、システムにソフトウェア修正を加える際に、すべてのチャンネルで既知の(決定論的な)位相を実現できる。この決定論的位相により、ICに接続されたフロントエンド・ネットワークの出力または入力で全チャンネルの同期を実現するために必要な、より広範なシステムレベルの校正アルゴリズムが簡素化される。この記事では、複数のデジタイザーIC、クロック・ソース、デジタル・インターフェースで構成される16チャンネルのレシーバー/トランスミッター・プラットフォームを使用して、このMCS機能を実証した実験結果を紹介します。

関連 コンテンツ

5Gアプリケーション

TDDおよびFDD構成のRadioThorium

このユースケースは、ベースバンド TDD および IF モード FDD 構成のための RadioThorium モジュールの手順とプロファイル設定の概要を説明します。

2024年2月24日

RF技術記事

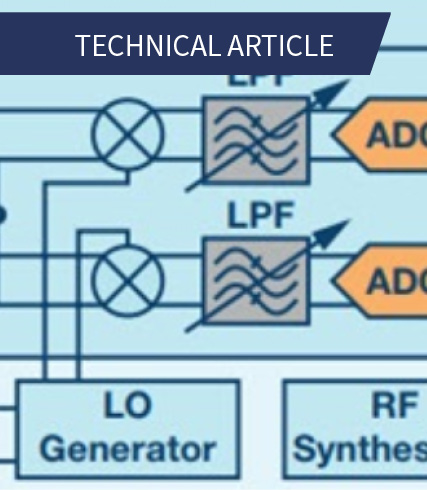

広帯域RFレシーバー・アーキテクチャ・オプションのレビュー

この記事では、ヘテロダイン受信機、ダイレクトサンプリング受信機という3つの一般的な受信機アーキテクチャの利点と課題を比較する。

2022年9月12日