Bauelemente mit breiter Bandlücke (WBG), wie Siliziumkarbid (SiC) und Galliumnitrid (GaN), haben Ähnlichkeiten mit siliziumbasierten MOSFETs und IGBTs, weisen aber unterschiedliche elektrische Eigenschaften auf, die spezielle Gate-Treiberlösungen erfordern. Dieser Artikel befasst sich mit den wichtigsten Anforderungen für die Entwicklung isolierter Gate-Treiber, die für WBG-Bauelemente optimiert sind, und hebt entscheidende Fortschritte hervor, die die Leistung, Effizienz und Zuverlässigkeit verbessern.

Autor

Michele Sclocchi

Anwendungsingenieur für Energie und Leistung

Südeuropa und Israel

Isolierungsanforderung

SiC-Bauelemente sind für den Betrieb bei hohen Spannungen über längere Zeiträume ausgelegt. Ein isolierter Gate-Treiber sorgt dafür, dass der Steuerschaltkreis vor diesen hohen Spannungen geschützt ist, was die allgemeine Zuverlässigkeit und Sicherheit des Systems erhöht.

Jedes Sicherheitsbauteil hat ein zeitabhängiges dielektrisches Durchschlagsprofil. Die Hersteller von isolierten Bauteilen stellen in der Regel Zertifizierungsnormen und Daten zum Isolationsprofil zur Verfügung.

Die Isolationswiderstandsspannung (VISO) wird durch die maximale Stehspannung bei einer Minute Dauer definiert, mit einem typischen Wert von 5,0 kVrms/1 min.

Die maximale Arbeitsisolation (VIOWM) ist die maximale Isolationsspannung, mit der das Gerät kontinuierlich betrieben werden kann, in der Regel mit einer erwarteten Lebensdauer von über 23 Jahren.

Abbildung 1 unten zeigt die Spannungslebensdauer des isolierten Produkts mit 5 kVrms von Skyworks bei verschiedenen Arbeitsspannungen; bei 1 kVrms beträgt die erwartete Lebensdauer 100 Jahre.1

Die maximale Überspannungsisolierung (VIOSM) dient der Simulation von Blitzeinschlägen. Es handelt sich um die strengste Hochspannungsisolationsprüfung, bei der eine vordefinierte Stoßimpulswellenform von 10 kV direkt an das Bauteil angelegt wird.

In den Industrienormen sind auch Mindestabstände zwischen metallischen Kontakten, die sich außerhalb der Isoliergeräte befinden, vorgeschrieben. Die Kriechstrecke ist definiert als der entlang der Oberfläche gemessene Abstand, und die Luftstrecke ist der kürzeste Abstand zwischen zwei leitenden Leitungen.

Die Mindestkriech- und Luftstrecken werden von den IEC-Normungsgremien als Richtwerte definiert, um Lichtbogenbildung während des Betriebs zu verhindern. Sie hängen von der Betriebsspannung, der Materialgruppe, der Klasse und der Technologie, den Umweltbedingungen, der Höhe und der Verschmutzung sowie der Verwendung der Geräte ab.

Einige Anwendungen erfordern auch verstärkte Isolierungen, die durch die Verwendung von zwei Isolierungsebenen in Reihe erreicht werden. Das bedeutet, dass bei einem Ausfall einer Ebene die zweite Ebene weiterhin einen Sicherheitsschutz bietet. Verstärkte Isolatoren sind Geräte, die eine Isolierung bieten, die der von zwei Basisisolatoren in Reihe entspricht.

Tabelle 1 fasst die typischen Isolationsspannungsspezifikationen der isolierten Treiber zusammen, die typischerweise für SiC- und GaN-Anwendungen vorgeschlagen werden.

Abbildung 1: Skyworks Digitaler Isolator Si86xxxD Zeitabhängiger dielektrischer Durchschlag

Kontinuierliche Fortschritte in der isolierten Gate-Treiber-Technologie sind für die erfolgreiche Integration von WBG-Bauteilen unerlässlich und ebnen den Weg für effizientere und zuverlässigere Leistungselektroniksysteme.

Hersteller | Teil Nummer | Isolationswert | Arbeitsspannung | Verstärkte Isolierung | Mindestkriechstrecke | Maximale Ausgangsspannung |

|---|---|---|---|---|---|---|

V Effektivwert | V (Spitze) | V (Spitze) | mm | V | ||

ADI | ADuM4146 | 5000 | 2150 | 8 | 30 | |

ADI | ADuM4121 | 5000 | 849 | 558 | 8 | 35 |

Skyworks | Si8281/2/3/4 | 5000 | 1400 | 840 | 8 | 30 |

Skyworks | Si8285 | 5000 | 1400 | 840 | 8 | 30 |

onsemi | NCD57084 | 2500 | 1200 | P | 8 | 36 |

onsemi | NCD57100 | 5000 | 1000 | P | 8 | 36 |

onsemi | NCP51752 | 3500 | 870 | P | 4 | 33 |

Skyworks | Si827x | 2500 | 849 | 155 | 3.9 | 30 |

Skyworks | Si82Fx | 6000 | 1860 | 849 | 8 | 30 |

ADI | MAX2270x | 5000 | 1000 | 8 | 28 |

Tabelle 1: Typische Isolationsspannungsspezifikationen von isolierten Treibern für SiC- und GaN-Anwendungen

Anforderungen an die Betriebsspannung2

Die Transkonduktanz eines MOSFET ist ein wichtiger Parameter für die Bestimmung der Schaltzeiten, da sie die Miller-Plateau-Gate-to-Source-Spannung während der Kommutierung beeinflusst.

Die Transkonduktanz (gfs) ist definiert als das Verhältnis zwischen der Änderung des Drainstroms und der Änderung der Gate-Spannung. Siliziumkarbid-MOSFETs haben im Vergleich zu Silizium-MOSFETs eine relativ geringere Steilheit (typischerweise 2,6 S gegenüber 15-20 S). Um diese geringere Transkonduktanz auszugleichen und eine große Änderung des Drainstroms zu erreichen, wird eine höhere Gate-Source-Spannung angelegt.

Darüber hinaus neigen SiC-MOSFETs dazu, über einen breiteren Vgs-Bereich im ohmschen Bereich zu bleiben, so dass ein schneller Übergang wichtig ist, um die Verluste zu minimieren.

Die auf dem Markt erhältlichen SiC-MOSFETs werden nach ihrer Schwellenspannung (VTH) eingeteilt. Die Schwellenspannung liegt typischerweise über 3,5 V; SiC-MOSFETs mit niedriger Schwellenspannung haben typische Werte im Bereich von 3 V bis 3,5 V. Die Schwellenspannung kann mit der Temperatur variieren und bis auf 1,8 V abfallen oder bis auf 4,3 V ansteigen.

Bei doppelseitigen Konfigurationen (High-Side- und Low-Side-MOSFETs), bei denen es zu einem Shoot-Through kommen kann, wird eine negative Gate-Vorspannung empfohlen, um eine ausreichende Sicherheitsmarge zu schaffen und parasitäres Einschalten zu verhindern, insbesondere bei hohen Schaltfrequenzen.

Die Gate-Betriebsspannung wird durch die Bewertung von Leistungsfaktoren wie Leitungsverluste (Rdson) und Schaltverluste innerhalb der empfohlenen Werte für die SiC-Gatespannung bestimmt.

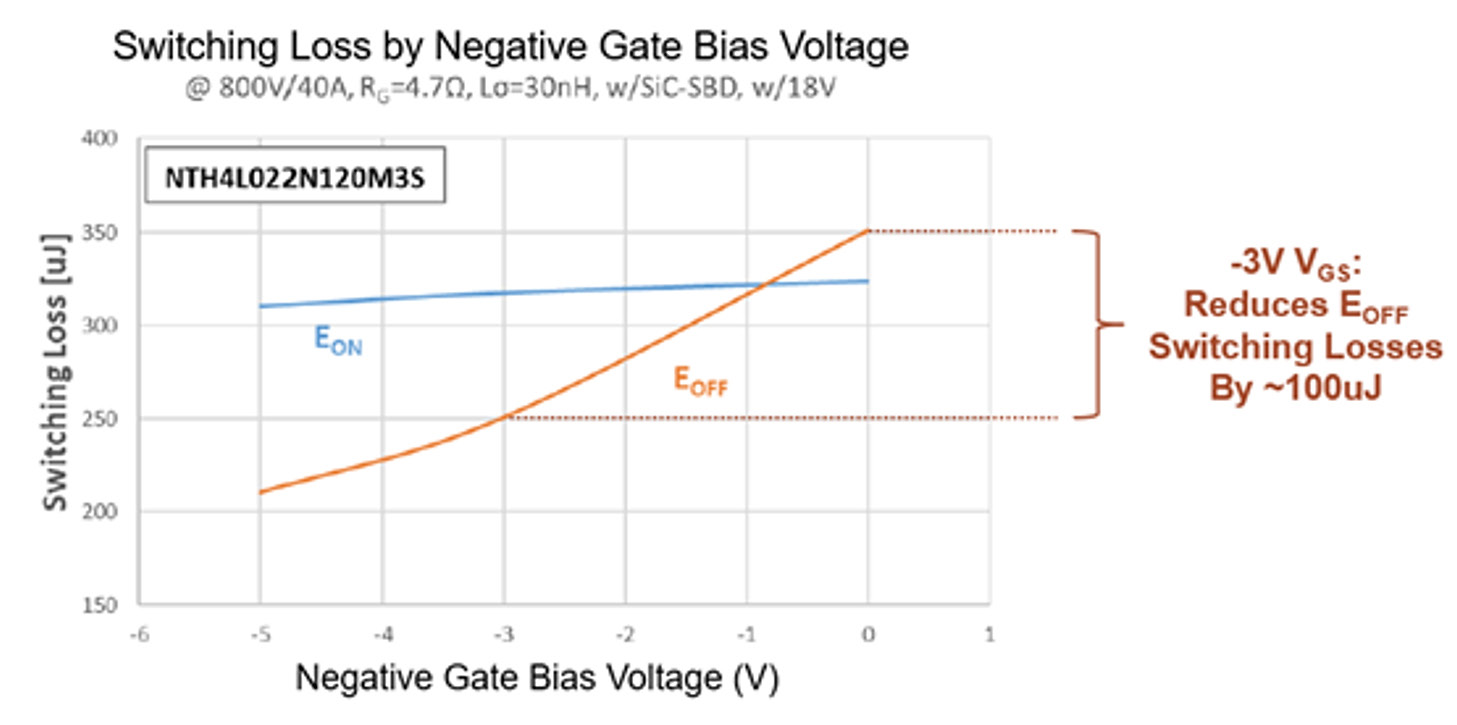

Abbildung 2 zeigt die Abschaltspannung mit negativer Vorspannung von 0 V bis -5 V (x-Achse) und die Schaltverluste (uJ) (y-Achse). Man beachte, dass die Abschaltverluste (Eoff) durch die Ansteuerung mit -3 V um 25 % reduziert werden.

Abbildung 2: ONSEMI SiC-Schaltverluste im Vergleich zur negativen Gate-Vorspannung (Quelle ONSEMI ND90204/D)

Unterspannungs-Lockout (UVLO)

Die Unterspannungsabschaltung (Undervoltage-Lockout) ist eine Funktion zum Schutz von Systemen im Falle eines Ausfalls der Vorspannungsversorgung. Die UVLO-Schaltung überwacht kontinuierlich die Gate-Versorgungsspannung und deaktiviert das Gate, wenn die Spannung unter einen bestimmten Schwellenwert fällt.

Siliziumkarbid-Treiber erfordern in der Regel einen höheren UVLO-Schwellenwert als Silizium-Bauelemente. Dedizierte SiC-Gate-Treiber enthalten häufig programmierbare UVLO-Stufen oder vordefinierte Optionen mit Schwellenwerten zwischen 10 V und 16 V. Der UVLO-Wert sollte deutlich über dem Miller-Plateaubereich (8-9 V) liegen und auf die thermischen Fähigkeiten des SiC-Bauelements abgestimmt sein.

Abbildung 3 zeigt die typischen Einschaltcharakteristiken eines SiC-MOSFET bei verschiedenen Gate-Source-Spannungen (Vgs). Wenn das System bei 150 A mit einer nominalen Gate-Spannung von 20 V arbeitet und der UVLO auf 15 V eingestellt ist, wird der Drain-Source-Spannungsabfall (Vds) auf einen minimalen Bruchteil eines Volt reduziert (von Punkt A nach Punkt B).

Wenn der UVLO-Wert jedoch unter 12 V liegt, ist der thermische Schutz unzureichend und führt zu einem Spannungsabfall, der mehr als doppelt so hoch ist wie erwartet (Punkt C).

Abbildung 3: Durchlassspannung eines SiC-MOSFET-Bauelements bei verschiedenen Gatespannungspegeln

Treiber-Spitzenstrom3

Der Spitzenstrom wird in den Datenblättern von Gate-Treibern oft hervorgehoben, aber seine Definition kann von Hersteller zu Hersteller variieren. In der Regel wird in den Datenblättern der Spitzenstrom als Sättigungsstrom definiert, der gemessen wird, indem entweder der Ausgang mit einer großen Kapazität kurzgeschlossen wird oder der Treiber kurzzeitig in einen Kurzschluss getrieben wird. Detaillierte I-U-Kurven, die die Mindest- und Höchstwerte bei verschiedenen Temperaturen und Herstellungsvarianten zeigen, sind jedoch selten enthalten.

Eine alternative Definition des Spitzenstroms beinhaltet die Angabe des maximalen Stroms innerhalb des linearen Bereichs der niedrigsten I-U-Kurve. Dieser konservative Ansatz stellt sicher, dass die Ausgangs-FETs des Gate-Treibers unter allen Temperatur- und Prozessbedingungen nicht in die Sättigung gehen, sofern der externe Gate-Widerstand richtig dimensioniert ist.

Über den Spitzenstromwert hinaus ist es wichtig, Spezifikationen wie den Sink- und Source-Widerstand der internen Schalter sowie die Anstiegs- und Abfallzeiten unter bestimmten Bedingungen zu berücksichtigen. Beispielsweise hat der Widerstand der internen Pull-up- und Pull-down-Schalter erhebliche Auswirkungen auf den durchschnittlichen Strom und die Verlustleistung im Treiber und im externen Gate-Widerstand.

Tabelle 2 fasst die Spannung, den Strom und die Geschwindigkeit verschiedener isolierter Gate-Treiber zusammen und hebt die Optionen hervor, die für typische SiC-Anwendungen geeignet sind.

Hersteller | Teil Nummer | Maximale Ausgangsspannung | I out peak (Quelle/Senke) | Rout (Quelle/Senke) Widerstand | Anstiegs-/Abfallzeit des Ausgangs | Ausbreitungsverzögerung (ns) |

|---|---|---|---|---|---|---|

V | A | Ω | nS | nsec | ||

ADI | ADuM4146 | 30 | 11 | 0.6 | 18 | 44 |

ADI | ADuM4121 | 35 | 2 | 1.8/1.6 | 18 | 53 |

Skyworks | Si8281/2/3/4 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 50 |

Skyworks | Si8285 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 40 |

onsemi | NCD57084 | 36 | 7 | 10 | 60 | |

onsemi | NCD57100 | 36 | 7 | 15 | 70 | |

onsemi | NCP51752 | 33 | 4.5/9 | 1.4/0.5 | 15/8 | 36 |

Skyworks | Si827x | 30 | 1.8/4.0 | 2.7/1.0 | 10/13 | 45 |

Skyworks | Si82Fx | 30 | 4 | 0.7 | 15 | 30 |

ADI | MAX2270x | 28 | 4/5.7 | 1.25 | 3.6/2.5 | 5 |

Gleichtaktstörfestigkeit (CMTI) und Isolationskapazität4

Die Gleichtaktstörfestigkeit (CMTI) ist ein Schlüsselfaktor bei der Auswahl isolierter Gate-Treiber. CMTI bezieht sich auf die höchstzulässige Änderungsrate der Gleichtaktspannung zwischen zwei isolierten Schaltkreisen. Im Allgemeinen sollte die CMTI-Bewertung für einen isolierten Gate-Treiber die maximale Schaltgeschwindigkeit der SiC-Bauelemente übertreffen. Bei einer typischen Schaltgeschwindigkeit von 50 V/nS sollte die CMTI-Bewertung über 100 V/ns liegen. Viele der neuesten Generationen von isolierten SiC- und GaN-Treibern haben CMTI-Werte von über 200 kV/uS.

Bei schnell schaltenden Bauelementen wie SiC und GaN mit Gate-Treibern mit niedrigem CMTI können verschiedene Probleme auftreten, z. B. Fehler, verpasste Impulse, erhöhte Ausbreitungsverzögerung und längere Totzeiten.

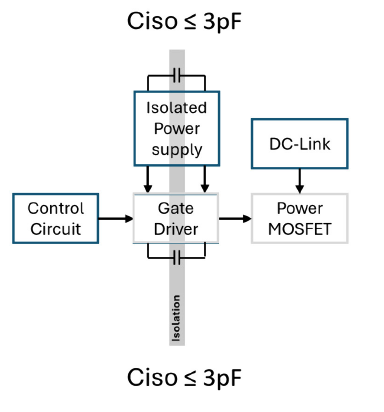

Ein weiterer wichtiger Faktor ist die parasitäre Isolationskapazität (Ciso), die in der Regel in einigen Picofarad zwischen dem Eingangssteuerpin und dem Ausgang gemessen wird. Bei einer SiC-Anwendung mit einer schnellen Übergangsrate von 100 V/ns und einer Isolationskapazität von 2 pF kann dies dazu führen, dass ein Strom von 200 mA über die Isolationsgrenze fließt.

Tabelle 3: Zusammenfassung typischer CMTI- und Isolationskapazitäten von isolierten Treibern für SiC- und GaN-Bauelemente

Diese Überlegung gilt auch für isolierte DC-DC-Wandler, die zur Versorgung des Bauelements mit den positiven und negativen Gate-Spannungen verwendet werden. Es ist wichtig, für SiC- und GaN-Anwendungen konzipierte Wandler mit sehr geringer Isolationskapazität zwischen Primär- und Sekundärseite auszuwählen. Die neue Familie der isolierten DC-DC-Wandler von RECOM (R12C2T25/R) weist beispielsweise eine Isolationskapazität von weniger als 3,5 pF auf.

Aktive Miller-Klemme

Bei Motorantrieben und anderen leistungselektronischen Systemen können Kurzschlussereignisse auftreten, so dass die Robustheit von SiC-MOSFETs in diesen Anwendungen ein wichtiges Anliegen ist. Unter Überstrombedingungen müssen SiC-MOSFETs gleichzeitig große Ströme und hohe Zwischenkreisspannungen für eine ausreichend lange Zeit verarbeiten, bis die Schutzschaltungen für die Kurzschlussreaktion aktiviert werden und das Gate-Steuersignal das Gerät abschaltet.

Die kritische Energie (Ec), ein wesentliches Maß für die Robustheit von Leistungsgeräten, bezieht sich auf die Mindestmenge an abgeleiteter Energie, die nach einem einzigen Kurzschluss zum Ausfall des geprüften Geräts führt.

Gerätehersteller geben in der Regel eine Kurzschlussfestigkeit an, die angibt, wie lange ein Gerät einen Kurzschluss aushalten kann, bevor es beschädigt wird.

Der Kurzschlussstrom wird durch Vds/Rdson und den Sättigungsstrom des Bauteils begrenzt, je nachdem, welcher Wert kleiner ist.

Aus der Literatur geht hervor, dass ein 1200-V-SiC-MOSFET bei einer Busspannung von 600 Vdc und einer Gate-Ansteuerung von 20 V bei Raumtemperatur einen Kurzschluss von 5-14 μs überstehen kann, was deutlich schlechter ist als bei Si-IGBT-Pendants.

Da SiC- und GaN-Bauteile kleine Chips haben, führt die höhere Stromdichte zu einem schnelleren Temperaturanstieg als bei Standard-Si-Bauteilen, was sich in einer kürzeren Zeit bis zum Ausfall niederschlägt und schnellere Schutzzeiten erforderlich macht.

In Abbildung 5 wird das Kurzschlussverhalten von zwei verschiedenen Schaltgeräten mit der gleichen Spannung und Stromstärke verglichen. Die Kurzschlussfestigkeit des IGBT (violette Kurve) beträgt etwa 38 Mikrosekunden im Vergleich zu den 8 Mikrosekunden des entsprechenden SiC-Bauteils (rote Kurve). Der Spitzenkurzschlussstrom des IGBT beträgt bis zu 200 Ampere, während er bei dem SiC-Bauelement fast doppelt so hoch ist.

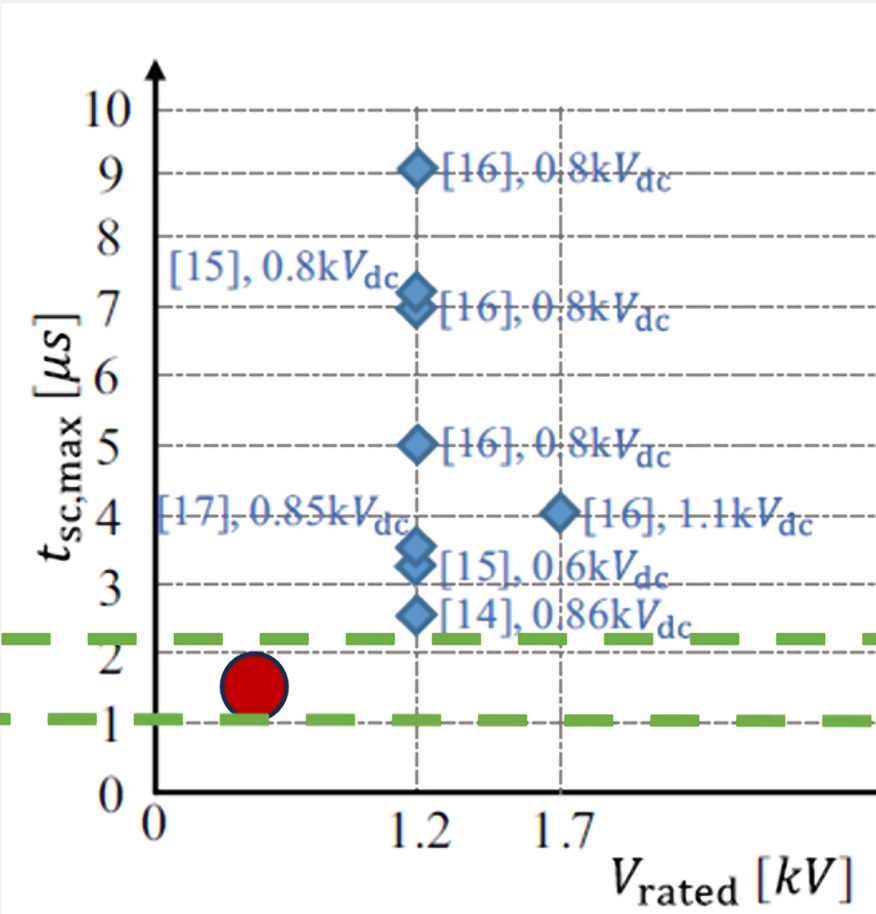

Der im Treiber implementierte Kurzschlussschutz sollte eine deutlich schnellere Reaktionszeit haben als die maximale Kurzschlussfestigkeit des SiC-Bauelements. Abbildung 6 fasst die maximale Kurzschluss-Ansprechzeit von SiC-Modulen in Abhängigkeit von ihrer Drain-Source-Nennspannung bei der angegebenen DC-Link-Spannung zusammen. Eine Kurzschlussreaktionszeit von unter 2 μs ist für einen einzelnen Kurzschluss relativ sicher. Im Allgemeinen steigt die Kurzschlussfestigkeit mit zunehmender Fläche und MOSFET-Kanallänge.6

Je kürzer die Kurzschlussreaktionszeit ist, desto größer ist die Fähigkeit des Bauelements, mehreren Kurzschlussereignissen standzuhalten. Es gibt jedoch keinen allgemein festgelegten Wert für die Kurzschlussfestigkeit; sie variiert je nach Faktoren wie Spannungsbus, Gehäuse-Die-Eigenschaften und Die-Fläche. Ein SiC-MOSFET in einem TO-247-Gehäuse hat zum Beispiel eine Kurzschlussfestigkeit von 1,7 μs bei 800 V und etwa 10 μs bei 400 V.

Abbildung 7 fasst die Ausfallzeiten der verschiedenen Leistungstransistortypen in Abhängigkeit von der Zwischenkreisspannung zusammen. Beachten Sie, dass die Ausfallzeiten von E-Mode-GaN-HEMTs viel geringer sind als die von Si- und SiC-MOSFETs.

Die gemessene Kurzschlussfestigkeit eines 650-V-GaN-Bauteils, das an einem Gleichspannungsbus von 400 V betrieben wird, beträgt etwa 630 ns.

Die Kurzschlussfestigkeit kann anhand der kritischen Energie (Ec) berechnet werden:

Abbildung 5: Kurzschlussstromvergleich des 1200 V/40 A SiC-MOSFET und des 1200 V/40 A Si IGBT bei Vds = 600 V und Tc = 25°C4

Abbildung 6: Kurzschluss-Ansprechzeit (SCRT) von SiC-Modulen

Abbildung 7: Ausfallzeit verschiedener Typen von Leistungstransistoren

Typisches SiC-MOSFET-Kurzschlussverhalten

Abbildung 8 zeigt die typischen Kurzschlusswellenformen einer zerstörungsfreien Prüfung mit niedriger Induktivität. Ein planarer SiC 1200 V mit einem auf 400 Vdc begrenzten DC-Bus wird einem Kurzschlusstest mit niedriger Induktivität (60 nH) unter Verwendung eines Kurzschlussimpulses von 2,2 μs unterzogen, um das Überleben des Geräts sicherzustellen. Die Wellenformen können in vier Phasen betrachtet werden:

- Phase A: Der SiC-MOSFET geht vom Sperrbereich in den ohmschen Bereich über. Der Strom beginnt aufgrund der geringen Schleifeninduktivität schnell anzusteigen. In diesem Fall beträgt das di/dt etwa 4 A/ns, was zu einem Strom von bis zu 1 kA innerhalb von 1 μs führt. Bei 1,1 μs, am Ende von Phase A, beträgt die Kurzschlussenergie etwa 0,4 J, was die maximale Verlustleistung des Geräts überschreitet. Daher sollte der Kurzschlussschutz

aktiviert werden, bevor das Gerät in den Sättigungsbereich eintritt. - Phase B: Der SiC-MOSFET tritt in den Sättigungsbereich ein, und die Kurzschlussenergie nimmt weiter zu.

- Phase C: Der SiC-MOSFET bleibt in der Sättigungszone. Die Erhöhung von Rds,on führt zu einem Absinken von Id von seinem Spitzenwert.

- Phase D: Wenn der SiC-MOSFET ausgeschaltet wird (wenn der Schutz aktiviert ist), führt das hohe dI/dt (33 A/ns) zu einer Überschreitung der Spitzenspannung

von 2,2 kV.

Der Kurzschlussschutz sollte innerhalb des grünen (linearen) Bereichs aktiviert werden, typischerweise innerhalb eines Zeitrahmens von 1-2 μs. Wenn der Kurzschluss erkannt wird, sollte der MOSFET mit einer kontrollierten Anstiegsrate ausgeschaltet werden (Soft-Switch-Funktion), um die Überschwinger zu minimieren.

Abbildung 9 zeigt die Widerstandszeit von planaren 700-V-SiC-MOSFETs von Microchip in Abhängigkeit von der Gate-to-Source-Spannung und dem Gleichspannungsbus. Wie erwartet, steigt die Widerstandszeit, wenn Vgs reduziert wird. Dies ermöglicht eine bessere Steuerung der Abschaltung des SiC-MOSFETs nach der Kurzschlusserkennung, um das Überschwingen zu minimieren (Soft-Turnoff). Eine bemerkenswerte Anwendung, bei der die überragende Widerstandszeit der planaren SiC-MOSFETs von Microchip sehr geschätzt wird, ist der Einsatz in Halbleiterschutzschaltern (SSCBs) oder E-Sicherungen.8

Abbildung 8: Typisches Kurzschlussverhalten von SiC-MOSFETs7

Abbildung 9: Microchip SiC-MOSFETs weisen Kurzschlusszeiten zwischen 3 μs und 14 μs auf, abhängig von der Zwischenkreisspannung und der angelegten Spannung Vgs

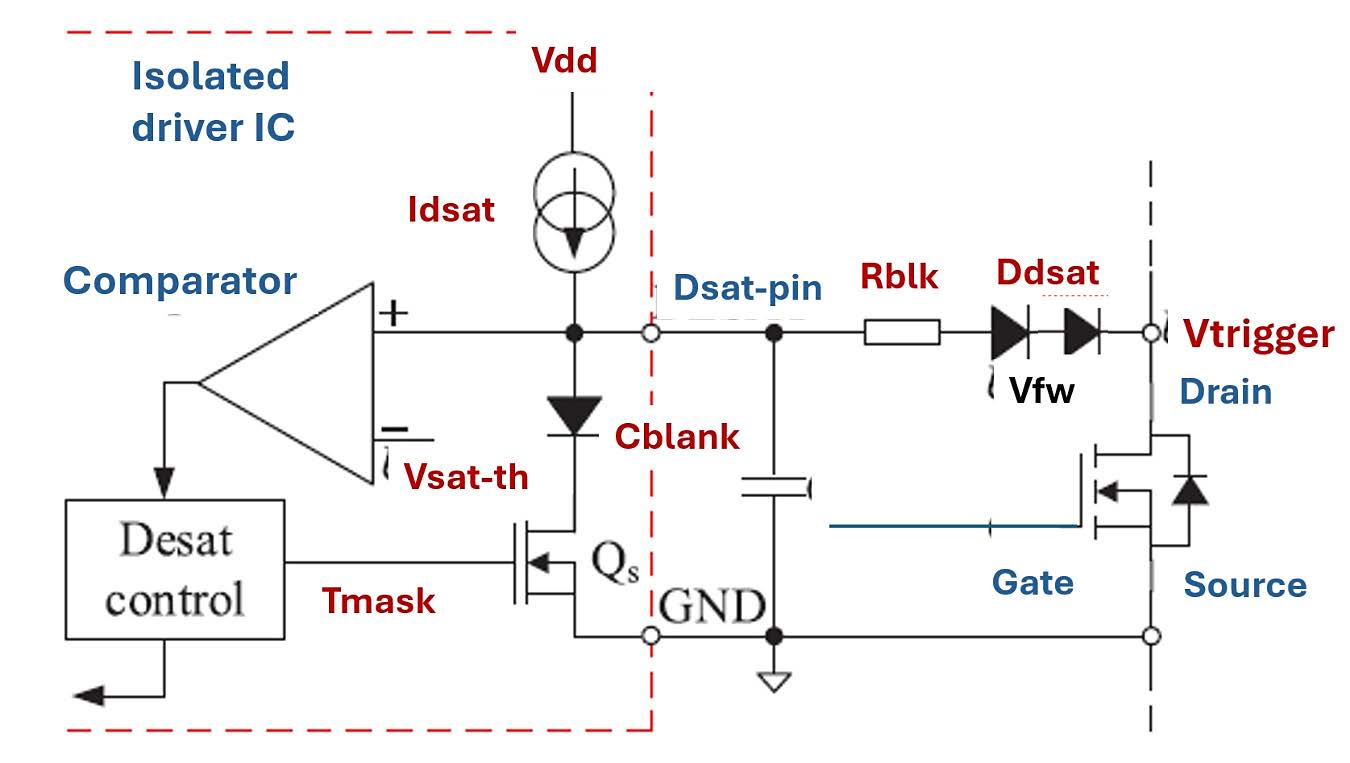

DESAT-Schutzschaltung9

Eine Entsättigungsschaltung (DESAT) ist eine weit verbreitete Methode zum Schutz vor Überstrom und Kurzschluss in IGBT-Schaltungen. Sie überwacht die Drain-Source-Spannung, wenn das Gerät voll eingeschaltet ist, und schaltet es automatisch ab, wenn ein Kurzschluss oder Überstrom festgestellt wird.

Isolierte Gate-Treiber mit integrierten DESAT-Schaltungen, die ursprünglich für IGBTs entwickelt wurden, können auch für SiC-MOSFETs und GaN-Bauelemente verwendet werden.

Wie in Abbildung 10 dargestellt, ist die DESAT-Schaltung in der Regel in den Gate-Treiber integriert und erfordert nur wenige externe Komponenten - eine schnelle Hochspannungsdiode (Ddsat) oder mehrere Dioden in Reihe, einen Austastkondensator (Cblank) und einen Widerstand (Rblk).

Wenn sich der MOSFET einschaltet, lädt eine Stromquelle (Idsat) den Kondensator auf, wodurch eine Austastperiode entsteht, die Fehlauslösungen beim Schalten verhindert. Die Diode wird in Durchlassrichtung vorgespannt, sobald die Spannung des Kondensators mit der Drain-Source-Spannung des MOSFETs übereinstimmt. Ein Kurzschluss wird ausgelöst, wenn die Drain-Source-Spannung (Vds) des MOSFET den Schutzschwellenwert (Vth-dsat) erreicht, abzüglich des Durchlassspannungsabfalls der Diode und der Spannung am Vorwiderstand (Idsat × Rdsat).

Abbildung 10: Typische DESAT-Schutzschaltung, die häufig in Gate-Treibern für IGBTs und SiC-MOSFETs zum Schutz vor Überstrom und Kurzschluss verwendet wird

Die Triggerspannung kann durch Anpassung des Widerstandswerts oder durch Verwendung mehrerer Dioden in Reihe verändert werden.

Normalerweise wird der DESAT-Auslösepunkt auf das Doppelte des maximalen Spitzenstroms eingestellt, er sollte jedoch sorgfältig auf den maximal gewünschten Strom während eines Kurzschlussereignisses abgestimmt werden.

Die DESAT-Diode muss ein schnell erholender Typ mit niedriger Sperrschichtkapazität sein, um die Störanfälligkeit durch schnelle Spannungsänderungen (dv/dt) zu minimieren.

Die Austastzeit ist so konfiguriert, dass eine falsche Triggerung während der Einschaltphase des MOSFETs verhindert wird und sich die Einschaltschwingungen beruhigen können. Sowohl die Triggerspannung (Vtrigger) als auch die Austastzeit sollten auf der Grundlage der spezifischen Eigenschaften und des Einschaltverhaltens des SiC-MOSFETs fein abgestimmt werden.

Es muss sichergestellt werden, dass die Gesamtenergie während eines Kurzschlusses unter einem Viertel der vom SiC-Hersteller angegebenen maximalen Stehvermögensenergie liegt.

Die DESAT-Schaltung ist einfach, leicht zu implementieren und hat einen minimalen Leistungsverlust. Bei der Verwendung von SiC-MOSFETs stellt sie jedoch gewisse Herausforderungen dar. Die Durchlassdiode muss hohen Spannungen standhalten und schnell reagieren, und die feste Austastzeit kann die Reaktion des Kurzschlussschutzes

verzögern.

Es ist zu beachten, dass die DESAT-Methode möglicherweise nicht unter allen Fehlerbedingungen eine gleichbleibende Genauigkeit bietet. Verschiedene Fehlerszenarien, wie z. B. hart schaltende Fehler oder Fehler unter Last, können zu unterschiedlichen Reaktionszeiten führen. Dennoch besteht das Hauptziel darin, katastrophale Geräteausfälle zu verhindern, selbst bei schnellen Stromstößen mit geringer Induktivität.

Beim Schutz eines typischen SiC-Moduls kann eine Abweichung von nur 0,5 V bei der DESAT-Schwellenspannung einen Unterschied von bis zu 100 A beim Drainstrom bedeuten.

Fehlerreaktionszeit für SiC-MOSFETs

Die Kurzschlussansprechzeit (SCRT) sollte bei SiC-MOSFETs auf 1 μs begrenzt sein. Die Gesamtansprechzeit des Schutzes, wie in Abbildung 11 dargestellt, ist die Summe von vier Komponenten:

- t_mask: Eine feste Zeit, während der der DESAT-Pin absichtlich niedrig gehalten wird (mit Masse verbunden), um ein falsches Auslösen der Schutzschaltung aufgrund von Spannungsspitzen während des anfänglichen Einschaltens des SiC-MOSFETs zu verhindern. Diese Zeit wird in der Regel zwischen 200-300 ns eingestellt.

- t_blank: Die Ladezeit des Kondensators C_blank durch die interne Stromquelle oder einen externen Widerstand.

- t_filter: Die typische interne Verzögerung zwischen dem Erreichen des Schwellenwerts der DESAT-Spannung und der Ausgabe des Abschaltbefehls an das Gate des MOSFETs.

- t_weich: Die Soft-Shutdown-Zeit, die hinzugefügt wird, um das Risiko von Überspannungsspitzen während des Abschaltvorgangs des SiC-MOSFETs zu verringern.

Die in Abbildung 12 gezeigte Wellenform wurde auf einem Prüfstand während eines hart geschalteten Fehlerszenarios aufgezeichnet, bei dem der MOSFET in einem Fehlerzustand eingeschaltet wird. In diesem Fall addiert die Austastzeit die gesamte Fehlererkennungszeit, gefolgt von der Rampenzeit, die in der Regel durch einen Pull-up-Widerstand definiert ist, der einen externen Kondensator auflädt. Diese Rampe wird fortgesetzt, bis die Spannung den Schwellenwert erreicht und die Soft-Shutdown-Sequenz auslöst.

Die untere gelbe Kurve zeigt, dass die Gate-Source-Spannung ansteigt, und wenn der Kurzschlussschutz aktiviert wird, geht er in den Soft-Shutdown-Modus über.

Wie bereits erwähnt, sollte die Gesamtreaktion der DESAT-Schaltung innerhalb von 1-2 usec liegen. Um die Erkennungszeit zu beschleunigen, ohne die Rauschimmunität des Dsat-Pins zu beeinträchtigen, ist es möglich, den internen Ladestrom des Cblank-Kondensators zu erhöhen, indem

eine externe Stromquelle hinzufügt. Um eine gute Rauschimmunität zu erhalten, sollte der Cblank-Kondensator einen Wert von über 300 pF haben.

Abbildung 13 zeigt die externe Schaltungskonfiguration, die verwendet werden kann, um eine schnellere Ladezeit für den Cblank-Kondensator zu erreichen, ohne seinen Kapazitätswert zu verringern. Diese Lösung kann auch für kaskadierte GaN-Bauelemente implementiert werden und ermöglicht eine Gesamtreaktionszeit von unter 400 ns.12

Abbildung 14 unten zeigt eine diskrete Kurzschlussschutzschaltung, die für eine schnelle Erkennung und einen schnellen Schutz optimiert ist und speziell für GaN-HEMT-Bauelemente entwickelt und getestet wurde. Diese Schaltung wurde mit einer Gesamtreaktionszeit von 122 ns getestet.13

Das Grundprinzip besteht darin, Vds-on am Gerät im eingeschalteten Zustand (Vsense) zu messen und mit einer Referenzspannung zu vergleichen. Wenn Vsense Vref überschreitet, liefert der Komparator ein hohes Fehlersignal (FLT). Das Abschaltsignal wird zum Zurücksetzen der Vsense-Spannung verwendet.

Bei Verwendung eines isolierten Treibers kann das FLT-Signal über einen Isolator an den Treiber zurückgeschickt werden. Das FLT-Signal an den Treiber kann den Gate-Treiber deaktivieren und eine harte Abschaltung des GaN-Bauelements erzwingen. Isolierte Treiber mit kurzer Ausbreitungsverzögerung sind vorzuziehen, um ultraschnelle Reaktionszeiten zu erreichen.

Abbildung 11: Reaktionszeit des Gesamtschutzes

Abbildung 12: Hard-Switch-Fehlerszenario eines SiC-Moduls mit isoliertem Gate-Treiber von Analog Devices.11 Die Gesamtreaktionszeit wird unter 1 μs gehalten.

Abbildung 13: Externe Schaltungskonfiguration für eine schnellere Ladezeit des Cblank-Kondensators, ohne den Kapazitätswert zu verringern

Abbildung 14: Ultraschnelle Ansprechzeit für GaN-HEMT-Bauelemente13

Gatestromanforderungen und Verlustleistung

Um die gewünschte Schaltgeschwindigkeit zu erreichen, ist es wichtig, einen Gate-Treiber mit einer angemessenen Treiberstromkapazität zu wählen.

Der Source- und Sink-Spitzenstrom lässt sich leicht berechnen, indem man die an der Gate-Source-Klemme anliegende Spannung (dVgdr) durch die Summe der Widerstandswerte teilt:

Rgin steht für den internen Gate-Widerstand des SiC-MOSFET, Rgonext und Rgoffext sind die externen Gate-Widerstände, die zur Steuerung der Ein- und Ausschaltgeschwindigkeit verwendet werden. Analog dazu bezeichnen Rgondriver und Rgoffdriver den Innenwiderstand des Gate-Treibers.

Um sicherzustellen, dass die externen Widerstände die Schaltgeschwindigkeiten effektiv regeln können, müssen der Quell- und der Senkenstrom innerhalb der Spitzenstromgrenzen des Treibers bleiben.

Um die Wärmeableitung zu verbessern und den Gate-Spitzenstrom in Hochfrequenz- oder Hochstrom-SiC-Anwendungen zu erhöhen, wird ein externer Totempol-Bipolartransistor empfohlen.

Abbildung 15 unten zeigt eine grundlegende Schaltung zur Treibererweiterung für den isolierten Treiber Si828x von Skyworks. Die Bipolartransistoren Q1 und Q2 regeln den Treiberstrom, der durch die Signale VH und VL gesteuert wird. Das Bild rechts zeigt einen Spitzen-Source-Strom von bis zu 30 A bei einer Gate-Kapazität von 220 pF.

Insbesondere bei großen Modulen trägt die externe Totempfahlschaltung zur Optimierung des Layouts und der Leistung bei, da die Transistoren näher am MOSFET-Gate platziert werden können. Dies minimiert die Induktivität des Gate-Schaltkreises und reduziert das potenzielle Klingeln am Gate-Pin des Bausteins. Außerdem verhindert die externe Schaltung ein Überschreiten der maximalen Verlustleistung des Treibers.

Der Gesamtleistungsbedarf des Gate-Schaltkreises wird durch Multiplikation der gesamten Gate-Ladung (Qg) des SiC-MOSFET mit der an den Gate-Source-Anschluss angelegten Spannung (dVgdr) und der Schaltfrequenz (fsw) ermittelt:

Schlussfolgerung

Insgesamt sind die kontinuierlichen Fortschritte in der isolierten Gate-Treiber-Technologie entscheidend für die erfolgreiche Integration von WBG-Bauelementen in verschiedene Anwendungen und ebnen den Weg für effizientere und zuverlässigere Leistungselektroniksysteme.

Referenzen

(*1) AN583 Safety Considerations and Layout Recommendations for Digital Isolators - Skyworks

(*2) ND90204 EliteSiC Gen 2 1200V MOFETs application note - ONSEMI

(*3) Peak Current of Isolated Gate Driver - Analog Devices

(*4) Review and analysis of SIC MOSFET's ruggdness and reliability - Jun Wang, Xi Jiang - Feb 2020

(*5) AN5355 Mitigation techniques of the SIC MOSFET gate voltage glitches with Miller clamp

(*6) Comparison and Discussion on Short-circuit Protection for SiC MOSFET Modules, Slavko Mocevic IEEE

(*7) Quelle: Neue Definition der kritischen Energie für die Robustheit von SiC-MOSFETs im Kurzschlussbetrieb.

(*8) Demonstrator der SiC-basierten E-Sicherungs-Hilfstechnologie für EV-Anwendungen - Microchip - PCIM Europe

(*9) AN1288: Si828x External Enhancement Circuit - Skyworks Ein verbessertes Entsättigungs-Kurzschluss-Schutzverfahren für SiC-Leistungsmodule science direct

(*10) Ein verbessertes Entsättigungs-Kurzschluss-Schutzverfahren für SiC-Leistungsmodule science direct (CPESE 2021)

(*11) Wolfspeed- Analog Device - Isolated Gate driver seminar

(*12) AN1288: Si828x External Enhancement Circuit- Skyworks

(*13) A Simple Desaturation Based Protection Circuit for GaN HEMT With Ultrafast response time - IEEE June 2021

(*14) AN1288 Si828x External Enhancement Cicuit - Skyworks DN80 - Bipolar transistors for MOSFET gate driving applications - Diodes