Los dispositivos de banda prohibida ancha (WBG), como los de carburo de silicio (SiC) y nitruro de galio (GaN), comparten similitudes operativas con los MOSFET e IGBT basados en silicio, pero presentan características eléctricas distintas que requieren soluciones especializadas de control de puerta. Este artículo explora los requisitos clave para diseñar controladores de puerta aislados optimizados para dispositivos WBG, destacando los avances críticos que mejoran el rendimiento, la eficiencia y la fiabilidad.

autor

Michele Sclocchi

Ingeniero de aplicaciones de energía y potencia

Europa del Sur e Israel

Requisitos de aislamiento

Los dispositivos SiC están diseñados para funcionar a altas tensiones durante periodos prolongados. Un controlador de puerta aislado garantiza que los circuitos de control estén protegidos de estas altas tensiones, lo que mejora la fiabilidad y seguridad generales del sistema.

Cada componente de seguridad tiene un perfil de ruptura dieléctrica dependiente del tiempo. Los fabricantes de componentes aislados suelen proporcionar normas de certificación y datos sobre el perfil de aislamiento.

La tensión soportada de aislamiento (VISO), se define por la tensión máxima soportada con un minuto de duración, con un valor típico de 5,0 kVrms/1 min.

El aislamiento máximo de trabajo (VIOWM) es la tensión de aislamiento máxima que el dispositivo puede funcionar de forma continua, normalmente con una vida útil prevista superior a 23 años.

La figura 1, a continuación, muestra la vida útil en tensión del producto aislado con 5 kVrms de Skyworks a diferentes tensiones de trabajo; a 1 kVrms, la vida útil prevista es de 100 años.1

La capacidad máxima de aislamiento contra sobretensiones (VIOSM) tiene por objeto simular la situación de un rayo. Se trata del ensayo de aislamiento de alta tensión más estricto, en el que se aplica directamente al componente una forma de onda de impulso de sobretensión predefinida de 10 kV.

Las normas industriales también especifican los requisitos mínimos de separación entre contactos metálicos externos a los dispositivos de aislamiento. La distancia de fuga se define como la distancia medida a lo largo de la superficie, y la separación es la distancia más corta entre dos conductores.

Las líneas de fuga y distancias mínimas son definidas por los organismos de normalización de la CEI a título orientativo, con el fin de evitar la formación de arcos eléctricos durante el funcionamiento. Dependen de la tensión de trabajo, el grupo de materiales, la clase y la tecnología, las consideraciones medioambientales, la altitud y la contaminación, y el uso del equipo.

Algunas aplicaciones también requieren aislamientos reforzados, que se consiguen utilizando dos niveles de aislamiento en serie. Esto significa que si falla una capa, la segunda sigue proporcionando protección de seguridad. Los aislamientos reforzados son dispositivos que proporcionan un aislamiento equivalente al de dos aislamientos básicos en serie.

La Tabla 1, a continuación, resume las especificaciones típicas de tensión de aislamiento de los controladores aislados sugeridos normalmente para aplicaciones SiC y GaN.

Figura 1: ruptura dieléctrica en función del tiempo del aislador digital Si86xxxD de Skyworks

Los continuos avances en la tecnología de controladores de puerta aislada son esenciales para integrar con éxito los dispositivos WBG, allanando el camino hacia sistemas de electrónica de potencia más eficientes y fiables.

Fabricante | Número de pieza | Capacidad de aislamiento | Tensión de trabajo | Aislamiento reforzado | Separación mínima | Tensión máxima de salida |

|---|---|---|---|---|---|---|

V rms | V (pico) | V (pico) | mm | V | ||

ADI | ADuM4146 | 5000 | 2150 | 8 | 30 | |

ADI | ADuM4121 | 5000 | 849 | 558 | 8 | 35 |

Skyworks | Si8281/2/3/4 | 5000 | 1400 | 840 | 8 | 30 |

Skyworks | Si8285 | 5000 | 1400 | 840 | 8 | 30 |

onsemi | NCD57084 | 2500 | 1200 | P | 8 | 36 |

onsemi | NCD57100 | 5000 | 1000 | P | 8 | 36 |

onsemi | NCP51752 | 3500 | 870 | P | 4 | 33 |

Skyworks | Si827x | 2500 | 849 | 155 | 3.9 | 30 |

Skyworks | Si82Fx | 6000 | 1860 | 849 | 8 | 30 |

ADI | MAX2270x | 5000 | 1000 | 8 | 28 |

Tabla 1: Especificaciones típicas de tensión de aislamiento de los controladores aislados para aplicaciones SiC y GaN

Requisitos de tensión de alimentación2

La transconductancia de un MOSFET es un parámetro importante para determinar los tiempos de conmutación, ya que influye en la meseta de Miller de la tensión puerta-fuente durante la conmutación.

La transconductancia (gfs) se define como la relación entre la variación de la corriente de drenaje y la variación de la tensión de puerta. Los MOSFET de carburo de silicio tienen una transconductancia relativamente menor que los de silicio (normalmente 2,6 S frente a 15-20 S, respectivamente). Para compensar esta menor transconductancia y conseguir un gran cambio en la corriente de drenaje, se aplica una tensión puerta-fuente más alta.

Además, los MOSFET de SiC tienden a permanecer en la región óhmica en un rango Vgs más amplio, por lo que es importante tener una transición rápida para minimizar las pérdidas.

Los MOSFET de SiC disponibles en el mercado se clasifican por su tensión umbral (VTH). Los de umbral alto tienen valores típicos superiores a 3,5 V; los MOSFET de SiC de umbral bajo tienen valores típicos que oscilan entre 3 V y 3,5 V. La tensión umbral puede variar con la temperatura, bajando hasta 1,8 V o subiendo hasta 4,3 V.

En configuraciones de doble terminación (MOSFET de lado alto y lado bajo), en las que pueden producirse disparos, se recomienda una polarización de puerta negativa para proporcionar un margen de seguridad suficiente y evitar el encendido parásito, especialmente a altas frecuencias de conmutación.

La tensión de conducción de la puerta operativa se determina evaluando factores de rendimiento como las pérdidas de conducción (Rdson) y las pérdidas de conmutación dentro de los valores recomendados de tensión de puerta de SiC.

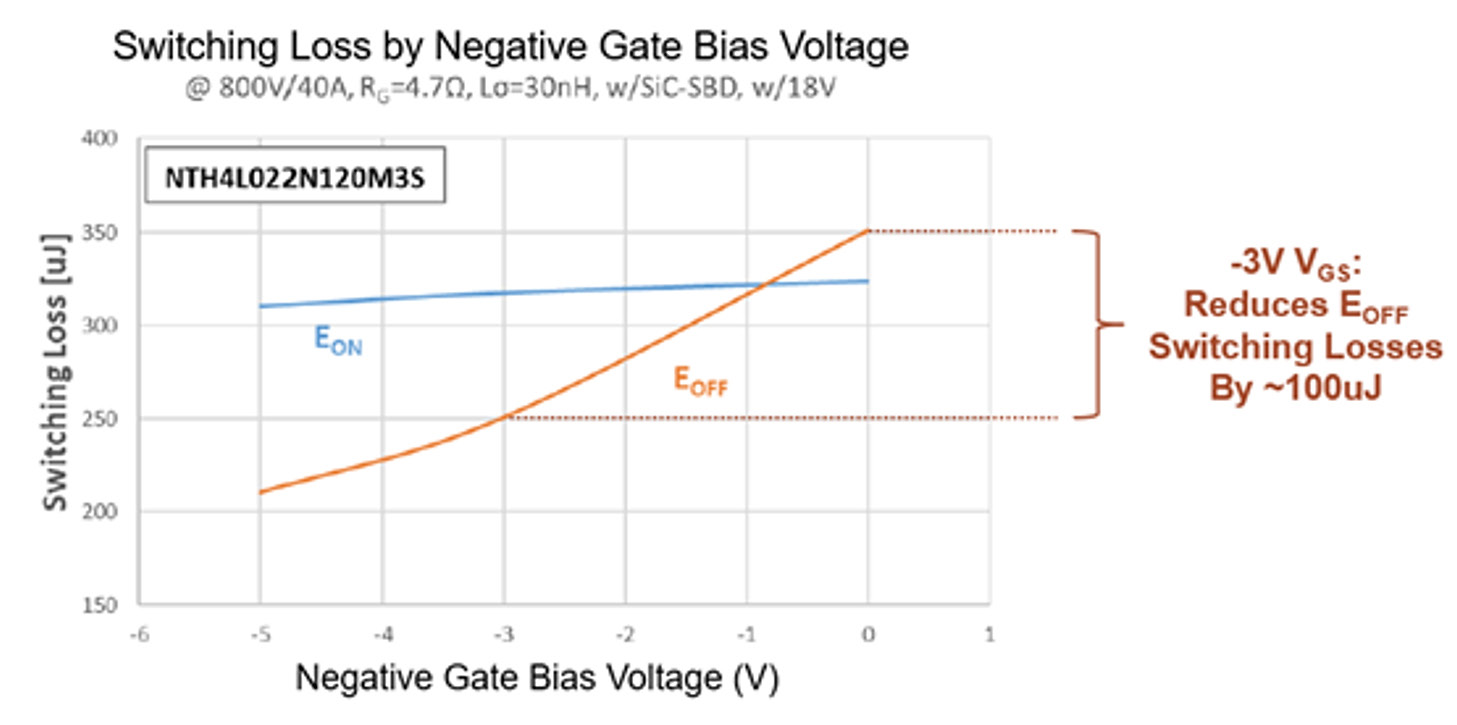

La figura 2 muestra la tensión de desconexión de polarización negativa de 0 V a -5 V (eje x) y las pérdidas de conmutación (uJ) (eje y). Obsérvese que el apagado con -3 V reduce las pérdidas por desconexión (Eoff) en un 25%.

Figura 2: Pérdida de conmutación de ONSEMI SiC frente a la tensión de polarización negativa de la puerta (fuente ONSEMI ND90204/D)

Bloqueo por subtensión (UVLO)

El bloqueo por subtensión es una función diseñada para proteger los sistemas en caso de fallo de la alimentación de polarización. El circuito UVLO supervisa continuamente la tensión de alimentación de la puerta y la desactiva si la tensión cae por debajo de un umbral definido.

Los controladores de carburo de silicio suelen requerir un umbral UVLO más alto que los dispositivos de silicio. Los controladores de puerta de SiC dedicados suelen incluir niveles UVLO programables u opciones predefinidas, con umbrales que oscilan entre 10 V y 16 V. El UVLO debe fijarse significativamente por encima de la región de meseta de Miller (8-9 V) y alinearse con las capacidades térmicas del dispositivo de SiC.

La figura 3 ilustra las características típicas de estado activado de un MOSFET de SiC a distintos niveles de tensión entre la puerta y la fuente (Vgs). Si el sistema funciona a 150 A con una tensión de puerta nominal de 20 V, y el UVLO se ajusta a 15 V, la caída de tensión de drenaje a fuente (Vds) se reduce a una fracción mínima de un voltio (del punto A al punto B).

Sin embargo, si el UVLO se ajusta por debajo de 12 V, la protección térmica se vuelve inadecuada, lo que provoca una caída de tensión de más del doble del nivel esperado (punto C).

Figura 3: Caída de tensión en estado encendido de un dispositivo MOSFET de SiC a diferentes niveles de tensión de puerta

Corriente de pico del conductor3

La corriente de pico se destaca a menudo en las hojas de datos de los controladores de puerta, pero su definición puede variar de un fabricante a otro. Normalmente, las hojas de datos definen la corriente de pico como la corriente de saturación, medida cortocircuitando la salida a una capacitancia grande o pulsando brevemente el controlador en un cortocircuito. Sin embargo, rara vez se incluyen curvas I-V detalladas que muestren los valores mínimos y máximos a distintas temperaturas y variaciones de fabricación.

Una definición alternativa de la corriente de pico consiste en especificar la corriente máxima dentro de la región lineal de la curva I-V más baja. Este enfoque conservador garantiza que los FET de salida del controlador de puerta permanezcan fuera de saturación en todas las condiciones de temperatura y proceso, siempre que la resistencia de puerta externa esté correctamente dimensionada.

Además del valor de la corriente de pico, es importante tener en cuenta especificaciones como la resistencia de origen y destino de los interruptores internos, y los tiempos de subida y bajada en condiciones específicas. Por ejemplo, la resistencia de los interruptores pull-up y pull-down internos influye significativamente en la corriente media y la disipación de potencia en el driver y la resistencia de puerta externa.

La Tabla 2 resume el voltaje, la corriente y la velocidad de varios controladores de puerta aislados, destacando las opciones que son adecuadas para las aplicaciones típicas de SiC.

Fabricante | Número de pieza | Tensión máxima de salida | I pico de salida (Fuente/Sumidero) | Resistencia de ruta (fuente/sumidero) | Tiempo de subida/caída de la salida | Retardo de propagación (ns) |

|---|---|---|---|---|---|---|

V | A | Ω | nS | nsec | ||

ADI | ADuM4146 | 30 | 11 | 0.6 | 18 | 44 |

ADI | ADuM4121 | 35 | 2 | 1.8/1.6 | 18 | 53 |

Skyworks | Si8281/2/3/4 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 50 |

Skyworks | Si8285 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 40 |

onsemi | NCD57084 | 36 | 7 | 10 | 60 | |

onsemi | NCD57100 | 36 | 7 | 15 | 70 | |

onsemi | NCP51752 | 33 | 4.5/9 | 1.4/0.5 | 15/8 | 36 |

Skyworks | Si827x | 30 | 1.8/4.0 | 2.7/1.0 | 10/13 | 45 |

Skyworks | Si82Fx | 30 | 4 | 0.7 | 15 | 30 |

ADI | MAX2270x | 28 | 4/5.7 | 1.25 | 3.6/2.5 | 5 |

Inmunidad transitoria en modo común (CMTI) y capacidad de aislamiento4

La inmunidad transitoria en modo común (CMTI) es un factor clave a la hora de elegir controladores de puerta aislados. La CMTI se refiere a la mayor velocidad de cambio permitida en la tensión de modo común entre dos circuitos aislados. Por lo general, la clasificación CMTI de un controlador de puerta aislado debe superar la velocidad de conmutación máxima de los dispositivos SiC. Con una velocidad de conmutación típica de 50 V/nS, el valor CMTI debería ser superior a 100 V/ns. Muchas de las generaciones más recientes de controladores aislados de SiC y GaN tienen valores CMTI superiores a 200 kV/uS.

Los dispositivos de conmutación rápida como SiC y GaN con controladores de puerta con CMTI bajo pueden experimentar varios problemas, como fallos, pulsos perdidos, mayor retardo de propagación y tiempo muerto prolongado.

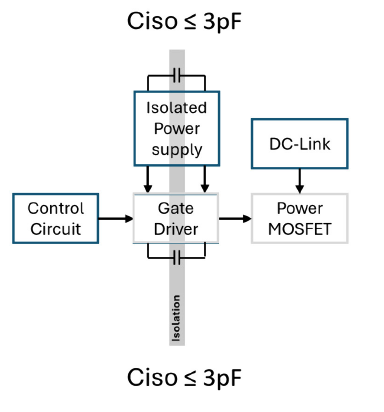

Otro factor importante a tener en cuenta es la capacitancia de aislamiento parásita (Ciso), que suele medirse en unos pocos picofaradios entre la patilla de control de entrada y la salida. En una aplicación de SiC con una velocidad de transición rápida de 100 V/ns y 2 pF de capacidad de aislamiento, esto puede dar lugar a 200 mA de corriente que fluye a través del límite de aislamiento.

Tabla 3: Resumen de la CMTI típica y la capacitancia de aislamiento de los controladores aislados para dispositivos SiC y GaN

Esta consideración también se aplica a los convertidores CC-CC aislados utilizados para suministrar las tensiones de puerta positiva y negativa al dispositivo. Es importante seleccionar convertidores diseñados para aplicaciones SiC y GaN con una capacitancia de aislamiento muy baja entre el primario y el secundario. Por ejemplo, la nueva familia de convertidores CC-CC aislados de RECOM (R12C2T25/R) presenta una capacitancia de aislamiento inferior a 3,5 pF.

Pinza Miller activa

En los sistemas de accionamiento de motores y otros sistemas electrónicos de potencia pueden producirse cortocircuitos, por lo que la robustez de los MOSFET de SiC es una de las principales preocupaciones en estas aplicaciones. En condiciones de sobrecorriente, los MOSFET de SiC deben manejar simultáneamente grandes corrientes y altas tensiones de bus de CC durante un tiempo suficientemente largo, hasta que se activan los circuitos de protección de respuesta al cortocircuito y la señal de control de puerta apaga el dispositivo.

La energía crítica (Ec), una métrica esencial de la robustez de los dispositivos de potencia, se refiere a la cantidad mínima de energía disipada que provoca el fallo del dispositivo probado tras un único evento de cortocircuito.

Los fabricantes de dispositivos suelen especificar una capacidad de resistencia a cortocircuitos, que es la cantidad de tiempo que un dispositivo puede soportar un cortocircuito antes de sufrir daños.

La corriente de cortocircuito está limitada por la Vds/Rdson y la corriente de saturación del dispositivo, la que sea menor.

Según la bibliografía, un MOSFET de SiC de 1200 V puede soportar un cortocircuito durante 5-14 μs con una tensión de bus de 600 Vcc y un accionamiento de puerta de 20 V a temperatura ambiente, lo que es mucho peor que los IGBT de Si.

Dado que los dispositivos de SiC y GaN tienen matrices pequeñas, la mayor densidad de corriente provoca un aumento más rápido de la temperatura en comparación con los dispositivos de Si estándar, lo que se traduce en un menor tiempo hasta el fallo y requiere tiempos de protección más rápidos.

La figura 5 compara el comportamiento en cortocircuito de dos dispositivos de conmutación con la misma tensión y corriente nominal. El tiempo de resistencia al cortocircuito del IGBT (curva morada) es de unos 38 microsegundos, frente a los 8 microsegundos del dispositivo de SiC equivalente (curva roja). La corriente de cortocircuito máxima del IGBT es de hasta 200 amperios, mientras que es casi el doble para el dispositivo de SiC.

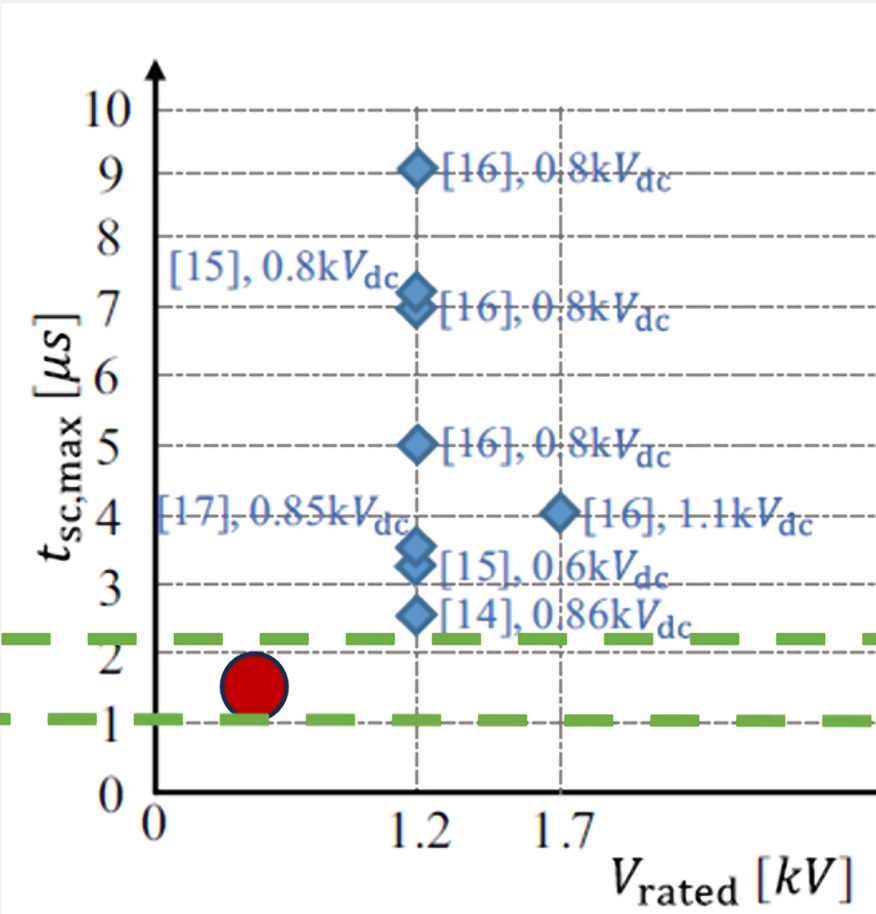

La protección contra cortocircuitos implementada en el excitador debe tener un tiempo de respuesta significativamente más rápido que el tiempo máximo de resistencia al cortocircuito del dispositivo de SiC. La figura 6, a continuación, resume el tiempo máximo de respuesta al cortocircuito de los módulos de SiC en función de su tensión nominal de drenaje a fuente con la tensión de enlace de CC indicada bajo prueba. Un tiempo de respuesta al cortocircuito inferior a 2 μs es relativamente seguro para un solo evento de cortocircuito. Por lo general, el tiempo de resistencia al cortocircuito aumenta con el área del dispositivo y la longitud del canal del MOSFET.6

Cuanto menor sea el tiempo de respuesta al cortocircuito, mayor será la capacidad del dispositivo para soportar múltiples cortocircuitos. Sin embargo, no existe un valor fijo universal para el tiempo de resistencia a cortocircuitos; varía en función de factores como el bus de tensión, las características del encapsulado y el área de la matriz. Por ejemplo, un MOSFET de SiC en un encapsulado TO-247 tiene un tiempo de resistencia al cortocircuito de 1,7 μs a 800 V y de aproximadamente 10 μs a 400 V.

La Figura 7 resume el tiempo de fallo de los distintos tipos de transistores de potencia en función de la tensión del bus de CC. Obsérvese que los tiempos de fallo de los HEMT de GaN en modo E son mucho menores que los de los MOSFET de Si y SiC.

El tiempo de resistencia al cortocircuito medido de un GaN de 650 V que funciona con un bus de tensión continua de 400 V es de unos 630 nseg.

El tiempo de resistencia al cortocircuito puede calcularse utilizando la energía crítica (Ec):

Figura 5: Comparación de la corriente de cortocircuito del MOSFET de SiC de 1200 V/40 A y del IGBT de Si de 1200 V/40 A a Vds = 600 V y Tc = 25°C4

Figura 6: Tiempo de respuesta al cortocircuito (SCRT) de los módulos de SiC

Figura 7: Tiempo de fallo de distintos tipos de transistores de potencia

Comportamiento típico del MOSFET de SiC en cortocircuito

La figura 8 muestra las formas de onda de cortocircuito típicas de una prueba no destructiva de baja inductancia. Un SiC 1200 V planar, con un bus de CC limitado a 400 Vcc, se somete a una prueba de cortocircuito de baja inductancia (60 nH) utilizando un impulso de cortocircuito de 2,2 μs para garantizar la supervivencia del dispositivo. Las formas de onda pueden verse en cuatro fases:

- Fase A: El MOSFET de SiC pasa de la región de corte a la región óhmica. La corriente empieza a aumentar rápidamente debido a la pequeña inductancia de bucle. En este caso, el di/dt es de unos 4 A/ns, lo que da lugar a una corriente de hasta 1 kA en 1 μs. A 1,1 μs, al final de la fase A, la energía de cortocircuito es de unos 0,4 J, lo que supera el límite máximo de disipación del dispositivo. Por lo tanto, la protección contra cortocircuitos

debe activarse antes de que el dispositivo entre en la región de saturación. - Fase B: El MOSFET de SiC entra en la región de saturación y la energía de cortocircuito sigue aumentando.

- Fase C: El MOSFET de SiC permanece en la región de saturación. El aumento de Rds,on provoca una caída de Id desde su pico.

- Fase D: Cuando el MOSFET SiC está apagado (cuando la protección está activada), el elevado dI/dt (33 A/ns) induce un pico de sobretensión

de 2,2 kV.

La protección contra cortocircuitos debe activarse dentro de la región verde (lineal), normalmente en un plazo de 1-2 μs. Cuando se detecta el cortocircuito, el MOSFET debe apagarse con una velocidad de giro controlada (función de conmutación suave) para minimizar los sobreimpulsos.

La figura 9 ilustra el tiempo de resistencia de los MOSFET SiC planares de 700 V de Microchip en función de la tensión puerta-fuente y del bus de tensión continua. Como era de esperar, el tiempo de resistencia aumenta cuando se reduce Vgs. Esto permite un mejor control del apagado del MOSFET de SiC tras la detección de cortocircuito para minimizar el sobreimpulso (apagado suave). Una aplicación notable en la que se valora mucho el tiempo de resistencia superior de los MOSFET SiC planares de Microchip es en los disyuntores de estado sólido (SSCB) o fusibles E.8

Figura 8: Comportamiento típico del MOSFET de SiC en cortocircuito7

Figura 9: Los MOSFET de SiC de Microchip presentan tiempos de resistencia al cortocircuito de entre 3 μs y 14 μs, en función de la tensión de enlace de CC y del Vgs aplicado.

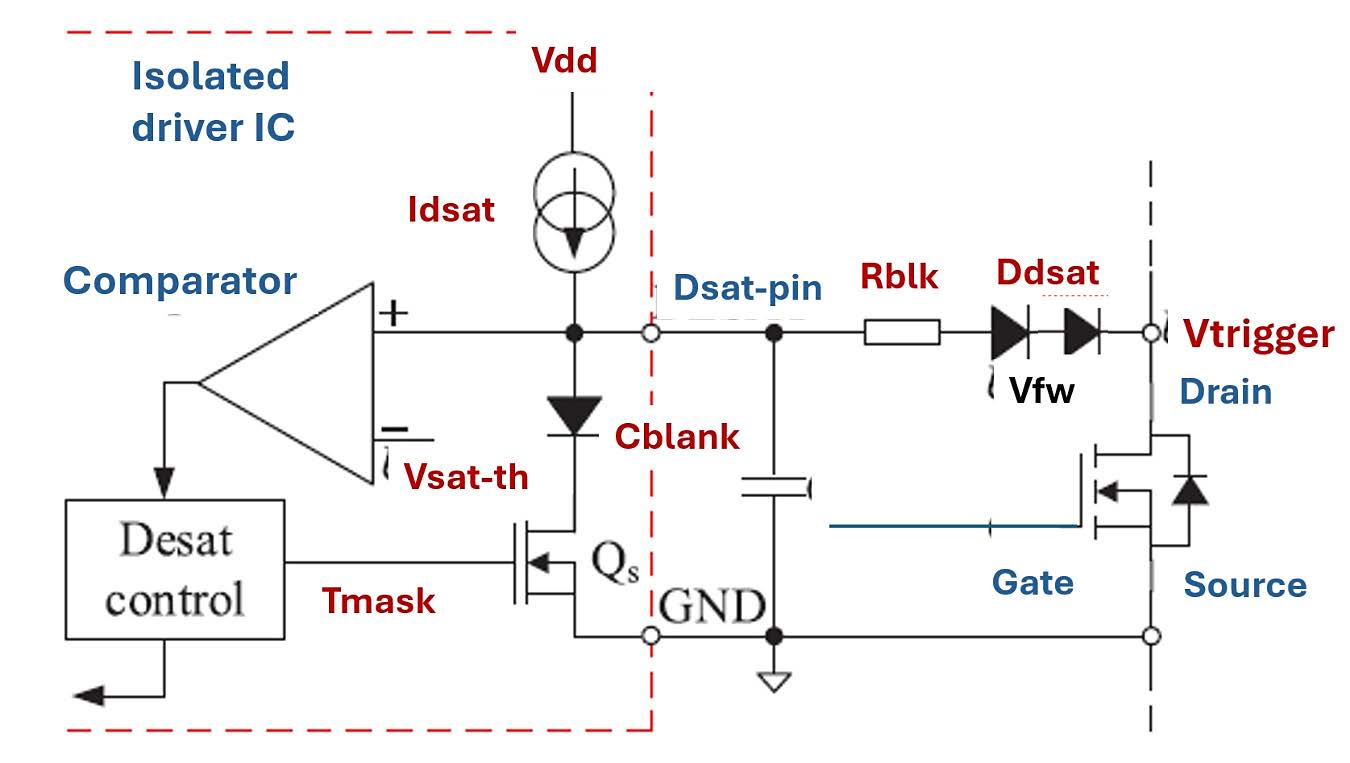

Circuito de protección DESAT9

Un circuito de desaturación (DESAT) es un método muy utilizado para la protección contra sobrecorrientes y cortocircuitos en circuitos IGBT. Funciona controlando la tensión drenaje-fuente cuando el dispositivo está totalmente encendido y lo desconecta automáticamente si detecta un cortocircuito o una sobrecorriente.

Los controladores de puerta aislados con circuitos DESAT incorporados, diseñados originalmente para IGBT, también pueden utilizarse con MOSFET de SiC y dispositivos de GaN.

Normalmente, como se muestra en la Figura 10, el circuito DESAT está integrado en el controlador de puerta, por lo que sólo requiere unos pocos componentes externos: un diodo rápido de alto voltaje (Ddsat) o varios diodos en serie, un condensador de supresión (Cblank) y una resistencia (Rblk).

Cuando el MOSFET se enciende, una fuente de corriente (Idsat) carga el condensador, creando un periodo de supresión para evitar falsos disparos durante la conmutación. El diodo pasa a polarización directa cuando la tensión del condensador coincide con la tensión de drenaje a fuente del MOSFET. Un cortocircuito se activa cuando la tensión drenaje-fuente (Vds) del MOSFET alcanza el umbral de protección (Vth-dsat), menos la caída de tensión hacia delante del diodo y la tensión a través de la resistencia en serie (Idsat × Rdsat).

Figura 10: Circuito de protección DESAT típico utilizado habitualmente en controladores de puerta para IGBT y MOSFET de SiC para proteger contra sobrecorriente y cortocircuito

Ajustar el valor de la resistencia o utilizar varios diodos en serie puede modificar la tensión de disparo.

Normalmente, el punto de disparo DESAT se establece en el doble de la corriente de pico máxima, pero debe ajustarse cuidadosamente a la corriente máxima deseada durante un evento de cortocircuito.

El diodo DESAT debe ser del tipo de recuperación rápida con baja capacitancia de unión para minimizar la susceptibilidad al ruido causado por los cambios rápidos de tensión (dv/dt).

El tiempo de supresión se configura para evitar falsos disparos durante la fase de encendido del MOSFET y para permitir que se estabilicen las oscilaciones de encendido. Tanto la tensión de disparo (Vtrigger) como el tiempo de supresión deben ajustarse con precisión en función de las características específicas y el comportamiento de encendido del MOSFET de SiC.

Es fundamental garantizar que la energía total durante un cortocircuito sea inferior a una cuarta parte de la energía de resistencia máxima especificada por el fabricante del SiC.

El circuito DESAT es sencillo, fácil de implementar y tiene una pérdida de potencia mínima. Sin embargo, presenta ciertos retos cuando se utiliza con MOSFETs de SiC. El diodo delantero debe soportar altas tensiones y responder con rapidez, y el tiempo de supresión fijo puede retrasar la respuesta de la protección contra cortocircuitos

.

Es importante señalar que el método DESAT puede no proporcionar una precisión consistente en todas las condiciones de fallo. Diferentes escenarios de fallo, como fallos de conmutación dura o fallos bajo carga, pueden dar lugar a tiempos de respuesta variables. No obstante, el objetivo principal es evitar el fallo catastrófico del dispositivo, incluso en presencia de sobrecorrientes rápidas de baja inductancia.

Por ejemplo, al proteger un módulo SiC típico, una variación de apenas 0,5 V en la tensión umbral DESAT puede corresponder a una diferencia de hasta 100 A en la corriente de drenaje.

Tiempo de respuesta a fallos de los MOSFET de SiC

El tiempo de respuesta al cortocircuito (SCRT) debe limitarse a 1 μs para los MOSFET de SiC. El tiempo de respuesta de protección total, como se ilustra en la Figura 11, es la suma de cuatro componentes:

- t_mask: Tiempo fijo durante el cual la patilla DESAT se mantiene intencionadamente baja (conectada a masa) para evitar falsos disparos del circuito de protección debidos a picos de tensión durante el encendido inicial del MOSFET de SiC. Este tiempo se ajusta típicamente entre 200-300 ns.

- t_blanco: El tiempo de carga del condensador C_blank a través de la fuente de corriente interna o de una resistencia externa.

- t_filtro: El retardo interno típico entre que la tensión DESAT alcanza su umbral y la emisión de la orden de apagado a la puerta del MOSFET.

- t_soft: El tiempo de apagado suave, que se añade para reducir el riesgo de picos de sobretensión durante el proceso de apagado del MOSFET de SiC.

La forma de onda que se muestra en la Figura 12, a continuación, se capturó en un banco durante un escenario de fallo de conmutación dura, en el que el MOSFET se enciende en una condición de fallo. En este caso, el tiempo de supresión añade el tiempo total de detección de fallos, seguido del tiempo de rampa, que normalmente se define mediante una resistencia de pull-up que carga un condensador externo. Esta rampa continúa hasta que la tensión alcanza el umbral, disparando la secuencia de apagado suave.

El trazo amarillo inferior muestra el aumento de la tensión puerta-fuente y, cuando se activa la protección contra cortocircuitos, pasa al modo de apagado suave.

Como se mencionó anteriormente, la reacción total del circuito DESAT debe estar dentro de 1-2 usec. Para acelerar el tiempo de detección sin comprometer la inmunidad al ruido de la patilla Dsat, es posible aumentar la corriente de carga interna del condensador Cblank añadiendo una fuente de corriente externa a

. Para mantener una buena inmunidad al ruido, el condensador Cblank debe tener un valor superior a 300 pF.

La figura 13 muestra la configuración del circuito externo que puede utilizarse para obtener un tiempo de carga más rápido para el condensador Cblank, sin reducir su valor de capacitancia. Esta solución también puede implementarse para dispositivos GaN en cascada, permitiendo un tiempo de respuesta total inferior a 400 ns.12

La figura 14, a continuación, muestra un circuito discreto de protección contra cortocircuitos optimizado para una detección y protección rápidas, diseñado y probado específicamente para dispositivos HEMT de GaN. Este circuito se ha probado con un tiempo de respuesta total de 122 ns.13

El principio básico es medir Vds-on a través del dispositivo en su estado encendido (Vsense) y compararlo con una tensión de referencia. Si Vsense supera Vref, el comparador proporciona una señal de fallo alta (FLT). La señal de apagado se utiliza para restablecer la tensión Vsense.

Si se utiliza un controlador aislado, la señal FLT puede enviarse de vuelta al controlador a través de un aislador. La señal FLT al controlador puede desactivar el controlador de puerta, forzando un apagado forzado del dispositivo GaN. Los controladores aislados con un retardo de propagación corto son preferibles para conseguir tiempos de respuesta ultrarrápidos.

Figura 11: Tiempo total de respuesta de la protección

Figura 12: Escenario de fallo de conmutación dura de un módulo SiC con controlador de puerta aislado de Analog Devices.11 El tiempo de respuesta total se mantiene por debajo de 1 μs.

Figura 13: Configuración del circuito externo para acelerar el tiempo de carga del condensador Cblank, sin reducir el valor de la capacitancia.

Figura 14: Tiempo de respuesta ultrarrápida de los dispositivos HEMT de GaN13

Requisitos de corriente de puerta y disipación de potencia

Para alcanzar la velocidad de conmutación deseada, es esencial elegir un controlador de puerta con una capacidad de corriente de accionamiento adecuada.

Los picos de corriente fuente y sumidero pueden calcularse fácilmente dividiendo la tensión aplicada a través del terminal puerta-fuente (dVgdr) por la suma de las resistencias de paso:

Rgin representa la resistencia de puerta interna del MOSFET de SiC, Rgonext y Rgoffext son las resistencias de puerta externas utilizadas para controlar las velocidades de encendido y apagado. Del mismo modo, Rgondriver y Rgoffdriver denotan la resistencia interna del controlador de puerta.

Para garantizar que las resistencias externas puedan regular eficazmente las velocidades de conmutación, la corriente de origen y de sumidero se mantienen dentro de los límites de corriente de pico del excitador.

Para mejorar la disipación del calor y aumentar la corriente de pico de la puerta en aplicaciones SiC de alta frecuencia o alta corriente, se recomienda utilizar un transistor bipolar tótem externo.

La Figura 15, a continuación, ilustra un circuito básico de mejora de conducción para el controlador aislado Si828x de Skyworks. Los transistores bipolares Q1 y Q2 regulan la corriente del excitador, controlada por las señales VH y VL. La imagen de la derecha ilustra una corriente pico de fuente de hasta 30 A con una capacitancia de puerta de 220 pF.

Especialmente en aplicaciones de módulos grandes, el circuito de tótem externo ayuda a optimizar el diseño y el rendimiento al permitir colocar los transistores más cerca de la puerta del MOSFET. De este modo se minimiza la inductancia del circuito de puerta y se reduce el potencial de zumbido en la patilla de puerta del dispositivo. Además, el circuito externo evita que se supere la capacidad máxima de disipación de potencia del excitador.

La potencia total requerida por el circuito de puerta se determina multiplicando la carga total de puerta (Qg) del MOSFET de SiC por la tensión aplicada a través del terminal puerta-fuente (dVgdr) y la frecuencia de conmutación (fsw):

Conclusión

En general, los continuos avances en la tecnología de controladores de puerta aislada son esenciales para integrar con éxito los dispositivos WBG en diversas aplicaciones, allanando el camino hacia sistemas electrónicos de potencia más eficientes y fiables.

Referencias

(*1) AN583 Safety Considerations and Layout Recommendations for Digital Isolators - Skyworks

(*2) ND90204 EliteSiC Gen 2 1200V MOFETs application note - ONSEMI

(*3) Peak Current of Isolated Gate Driver - Analog Devices

(*4) Review and analysis of SIC MOSFET's ruggdness and reliability - Jun Wang, Xi Jiang - Feb 2020

(*5) AN5355 Mitigation techniques of the SIC MOSFET gate voltage glitches with Miller clamp

(*6) Comparison and Discussion on Short-circuit Protection for SiC MOSFET Modules, Slavko Mocevic IEEE

(*7) Fuente: Nueva definición de energía crítica para la robustez de los MOSFET de SiC en cortocircuito.

(*8) SiC-Based Auxiliary E-Fuse Technology Demonstrator for EV Applications - Microchip - PCIM Europe

(*9) AN1288: Si828x External Enhancement Circuit - Skyworks Método mejorado de protección contra cortocircuitos por desaturación para módulos de potencia de SiC science direct

(*10) Método mejorado de protección contra cortocircuitos por desaturación para módulos de potencia de SiC science direct (CPESE 2021)

(*11) Wolfspeed- Analog Device - Isolated Gate driver seminar

(*12) AN1288: Si828x External Enhancement Circuit- Skyworks

(*13) A Simple Desaturation Based Protection Circuit for GaN HEMT With Ultrafast response time - IEEE June 2021

(*14) AN1288 Si828x External Enhancement Cicuit - Skyworks DN80 - Bipolar transistors for MOSFET gate driving applications - Diodos