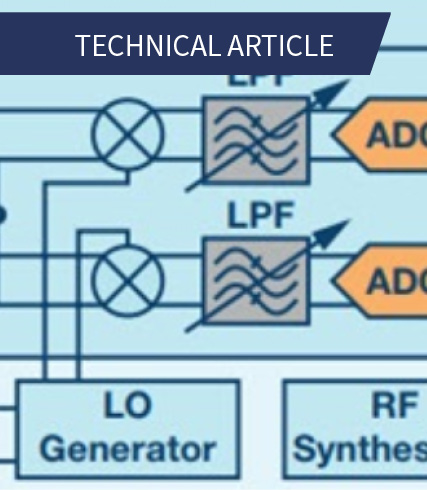

将多个数字信号处理 (DSP) 块、宽带数模转换器 (DAC) 和宽带模数转换器 (ADC) 集成到单个单片芯片中,现在可以卸载功耗高的 FPGA 资源,从而实现占地面积更小、功耗更低、通道数更多的平台,其采样率比以前更高。伴随这一新功能而来的是这些集成电路 (IC) 中的新型多芯片同步 (MCS) 算法,它允许用户在为系统供电或以其他方式对系统进行软件修改时,实现所有通道的已知(确定)相位。因此,这种确定的相位简化了更广泛的系统级校准算法,以实现连接到这些集成电路的前端网络输出或输入端的所有通道的同步。本文介绍的实验结果表明了这种 MCS 功能,同时使用了由多个数字化集成电路、时钟源和数字接口组成的 16 通道接收器/发射器平台。