Wide bandgap (WBG) devices, such as silicon carbide (SiC) and gallium nitride (GaN), share operational similarities with silicon-based MOSFETs and IGBTs but exhibit distinct electrical characteristics that require specialized gate-driving solutions. This article explores key requirements for designing isolated gate drivers optimized for WBG devices, highlighting critical advancements that enhance performance, efficiency and reliability.

author

Michele Sclocchi

Energy & Power Application Engineer

South Europe & Israel

Isolation Requirement

SiC devices are designed to operate at high voltages over extended periods. An isolated gate driver ensures that the control circuitry is protected from these high voltages, enhancing the overall reliability and safety of the system.

Every safety component has a time dependent dielectric breakdown profile. Manufacturers of isolated components usually provide certification standards and isolation profile data.

The isolation withstand voltage (VISO), is defined by the maximum withstand voltage with one minute duration, with a typical value of 5.0 kVrms/1 min.

The maximum working isolation (VIOWM) is the maximum isolation voltage that the device can operate continuously, usually with an expected lifetime above 23 years.

Figure 1, below, shows the voltage lifetime of the isolated product with 5 kVrms from Skyworks at different working voltages; at 1 kVrms, the expected lifetime is 100 years.1

The maximum surge isolation rating (VIOSM) is intended to simulate the lightning condition. It is the most stringent high voltage isolation test, where a 10 kV predefined surge pulse waveform is applied directly to the component.

Industry standards also specify minimum spacing requirements between metallic contacts that are external to the isolation devices. Creepage is defined as the distance measured along the surface, and clearance is the shortest distance between two conductive leads.

Minimum creepage and clearance are defined by the IEC standard bodies as guidance, intended to prevent arcing during operation. They depend on working voltage, material group, class and technology, environmental consideration, altitude and pollution, and equipment use.

Some applications also require reinforced isolations, achieved by using two levels of isolation in series. This means that if one layer fails, the second layer still provides safety protection. Reinforced isolators are devices that provide insulation equivalent to two basic isolators in series.

Table 1, below, summarizes the typical isolation voltage specifications of the isolated drivers typically suggested for SiC and GaN applications.

Figure 1: Skyworks digital isolator Si86xxxD time-dependent dielectric breakdown

Ongoing advancements in isolated gate driver technology are essential for the successful integration of WBG devices, paving the way for more efficient and reliable power electronics systems.

Manufacturer | Part Number | Insulation Rating | Working Voltage | Reinforced Isolation | Minimum Creepage | Maximum Output Voltage |

|---|---|---|---|---|---|---|

V rms | V (peak) | V (peak) | mm | V | ||

ADI | ADuM4146 | 5000 | 2150 | 8 | 30 | |

ADI | ADuM4121 | 5000 | 849 | 558 | 8 | 35 |

Skyworks | Si8281/2/3/4 | 5000 | 1400 | 840 | 8 | 30 |

Skyworks | Si8285 | 5000 | 1400 | 840 | 8 | 30 |

onsemi | NCD57084 | 2500 | 1200 | P | 8 | 36 |

onsemi | NCD57100 | 5000 | 1000 | P | 8 | 36 |

onsemi | NCP51752 | 3500 | 870 | P | 4 | 33 |

Skyworks | Si827x | 2500 | 849 | 155 | 3.9 | 30 |

Skyworks | Si82Fx | 6000 | 1860 | 849 | 8 | 30 |

ADI | MAX2270x | 5000 | 1000 | 8 | 28 |

Table 1: Typical isolation voltage specifications of isolated drivers for SiC and GaN applications

Driving voltage requirements2

The transconductance of a MOSFET is an important parameter for determining switching times, as it influences the Miller plateau gate-to-source voltage during commutation.

Transconductance (gfs) is defined as the ratio of the change in drain current to the change in gate voltage. Silicon carbide MOSFETs have a relatively lower transconductance compared to silicon MOSFETs (typically 2.6 S versus 15–20 S, respectively). To compensate for this lower transconductance and achieve a large change in drain current, a higher gate-to-source voltage is applied.

Additionally, SiC MOSFETs tends to stay in the ohmic region over a broader Vgs range, so it is important to have a fast transition to minimize the losses.

SiC MOSFETs available on the market are categorized by their threshold voltage (VTH). High-threshold has typical values above 3.5 V; low-threshold SiC MOSFETs have typical values ranging from 3 V to 3.5 V. The threshold voltage can vary with temperature, dropping as low as 1.8 V or rising as high as 4.3 V.

In double-ended configurations (high-side and low-side MOSFETs), where shoot-through may occur, a negative gate bias is recommended to provide a sufficient safety margin and prevent parasitic turn-on, especially at high switching frequencies.

The operating gate driving voltage is determined by evaluating performance factors such as conduction losses (Rdson) and switching losses within the SiC gate voltage recommended values.

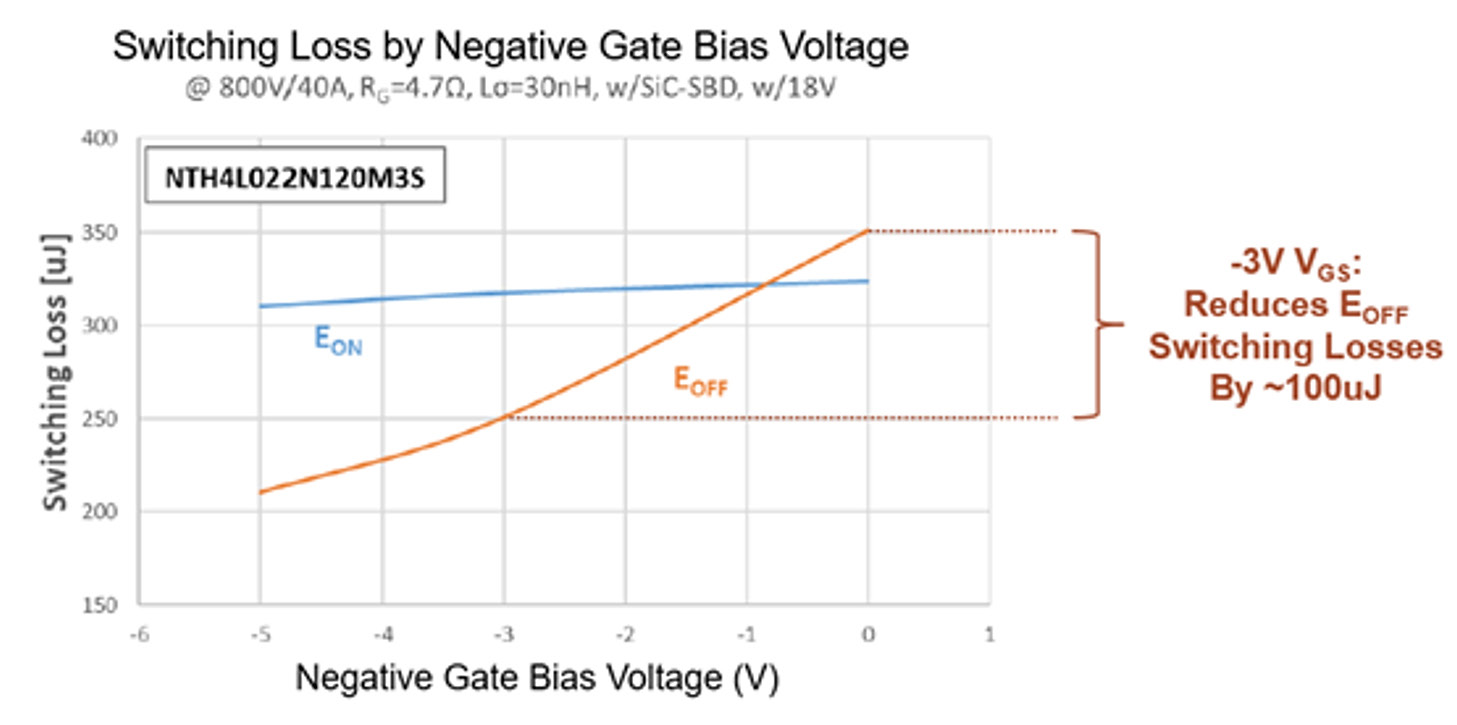

Figure 2, shows negative bias turnoff voltage from 0 V to -5 V (x-axis) and switching losses (uJ) (y-axis). Note that driving the turnoff with -3 V reduces the switching off (Eoff) losses by 25%.

Figure 2: ONSEMI SiC switching loss versus negative gate bias voltage (source ONSEMI ND90204/D)

Undervoltage-lockout (UVLO)

Undervoltage-lockout is a feature designed to protect systems in the event of a bias supply failure. The UVLO circuit continuously monitors the gate supply voltage and disables the gate if the voltage drops below a defined threshold.

Silicon carbide drivers typically require a higher UVLO threshold than silicon devices. Dedicated SiC gate drivers often include programmable UVLO levels or predefined options, with thresholds ranging from 10 V to 16 V. The UVLO should be set significantly above the Miller plateau region (8–9 V) and aligned with the thermal capabilities of the SiC device.

Figure 3 illustrates the typical on-state characteristics of a SiC MOSFET at various gate-to-source voltage (Vgs) levels. If the system operates at 150 A with a nominal gate voltage of 20 V, and the UVLO is set to 15V, the drain-to-source voltage drop (Vds) is reduced to a minimal fraction of a volt (from point A to point B).

However, if the UVLO is set below 12 V, thermal protection becomes inadequate, leading to a voltage drop more than twice the expected level (point C).

Figure 3: On-state drop voltage of a SiC MOSFET device at different

gate voltage levels

Driver Peak Current3

Peak current is often highlighted in gate driver datasheets, but its definition can vary among manufacturers. Typically, datasheets define peak current as the saturation current, measured by either shorting the output to a large capacitance or briefly pulsing the driver into a short circuit. However, detailed I-V curves showing minimum and maximum values across various temperatures and manufacturing variations are rarely included.

An alternative definition of peak current involves specifying the maximum current within the linear region of the lowest I-V curve. This conservative approach ensures the gate driver’s output FETs stay out of saturation under all temperature and process conditions, provided the external gate resistor is correctly sized.

Beyond the peak current value, it is important to consider specifications like the sink and source resistance of the internal switches, and the rise- and fall-times under specific conditions. For example, the resistance of the internal pull-up and pull-down switches significantly impacts the average current and power dissipation in the driver and external gate resistor.

Table 2 summarizes the voltage, current and speed of various isolated gate drivers, highlighting options that are suitable for typical SiC applications.

Manufacturer | Part Number | Maximum Output Voltage | I out peak (Source/Sink) | Rout (Source/Sink) resistance | Output rise/fall time | Propagation delay (ns) |

|---|---|---|---|---|---|---|

V | A | Ω | nS | nsec | ||

ADI | ADuM4146 | 30 | 11 | 0.6 | 18 | 44 |

ADI | ADuM4121 | 35 | 2 | 1.8/1.6 | 18 | 53 |

Skyworks | Si8281/2/3/4 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 50 |

Skyworks | Si8285 | 30 | 2.7/5.5 | 2.48/ 0.86 | 5.5 | 40 |

onsemi | NCD57084 | 36 | 7 | 10 | 60 | |

onsemi | NCD57100 | 36 | 7 | 15 | 70 | |

onsemi | NCP51752 | 33 | 4.5/9 | 1.4/0.5 | 15/8 | 36 |

Skyworks | Si827x | 30 | 1.8/4.0 | 2.7/1.0 | 10/13 | 45 |

Skyworks | Si82Fx | 30 | 4 | 0.7 | 15 | 30 |

ADI | MAX2270x | 28 | 4/5.7 | 1.25 | 3.6/2.5 | 5 |

Common-mode transient immunity (CMTI) and isolation capacitance4

Common-mode transient immunity (CMTI) is a key factor when choosing isolated gate drivers. CMTI refers to the highest permissible rate of change in common-mode voltage between two isolated circuits. Generally, the CMTI rating for an isolated gate driver should surpass the maximum switching speed of the SiC devices. With a typical switching speed of 50 V/nS, the CMTI rating should be above 100 V/ns. Many of the newest generations of isolated SiC and GaN drivers have CMTI values above 200 kV/uS.

Fast-switching devices like SiC and GaN with gate drivers with low CMTI may experience various issues, such as faults, missed pulses, increased propagation delay, and extended dead-time.

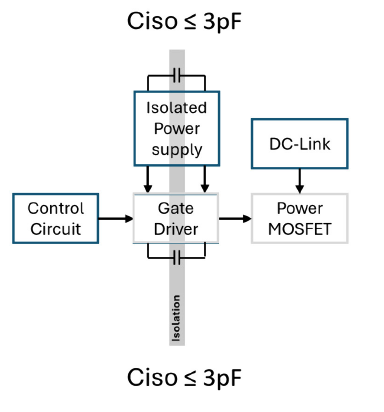

Another important factor to consider is the parasitic isolation capacitance (Ciso), usually measured in a few picofarads between the input control pin and the output. In a SiC application with a rapid transition rate of 100 V/ns and 2 pF of isolation capacitance, this can result in 200 mA of current flowing across the isolation boundary.

Table 3: Summary of typical CMTI and isolation capacitance of isolated drivers for SiC and GaN devices

This consideration also applies to isolated DC-DC converters used to supply the positive and negative gate voltages to the device. It is important to select converters designed for SiC and GaN applications with very low isolation capacitance between primary and secondary. For example, the new family of isolated DC-DC converters from RECOM (R12C2T25/R) features an isolation capacitance of less than 3.5 pF.

Active Miller clamp

Short-circuit events may occur in motor driving and other power electronics systems, making the ruggedness of SiC MOSFETs a major concern in these applications. In overcurrent conditions, SiC MOSFETs must simultaneously handle large currents and high DC bus voltages for a sufficiently long time, until the short-circuit response protection circuits activate and the gate control signal shuts down the device.

Critical energy (Ec), an essential metric of robustness for power devices, refers to the minimum amount of dissipated energy that leads to the failure of the tested device after a single short-circuit event.

Device manufacturers typically specify a short-circuit withstand capacity, which is the amount of time a device can handle a short-circuit event before sustaining damage.

The short-circuit current is limited by the Vds/Rdson and the device saturation current, whichever is smaller.

According to reported literature, a 1200 V SiC MOSFET can withstand a short-circuit event for 5-14 μs under a 600 Vdc bus voltage and a gate drive of 20 V at room temperature, which is significantly worse than Si IGBT counterparts.

Since SiC and GaN devices have small dies, the higher current density causes a faster temperature rise compared to standard Si devices, translating into a shorter time-to-failure and necessitating faster protection times.

Figure 5, compares the short-circuit behavior of two different switching devices with the same voltage and current rating. The short-circuit withstand time of the IGBT (purple curve) is around 38 microseconds compared to the 8 microseconds of the equivalent SiC device (red curve). The peak short-circuit current of the IGBT is up to 200 amps, while it is almost double for the SiC device.

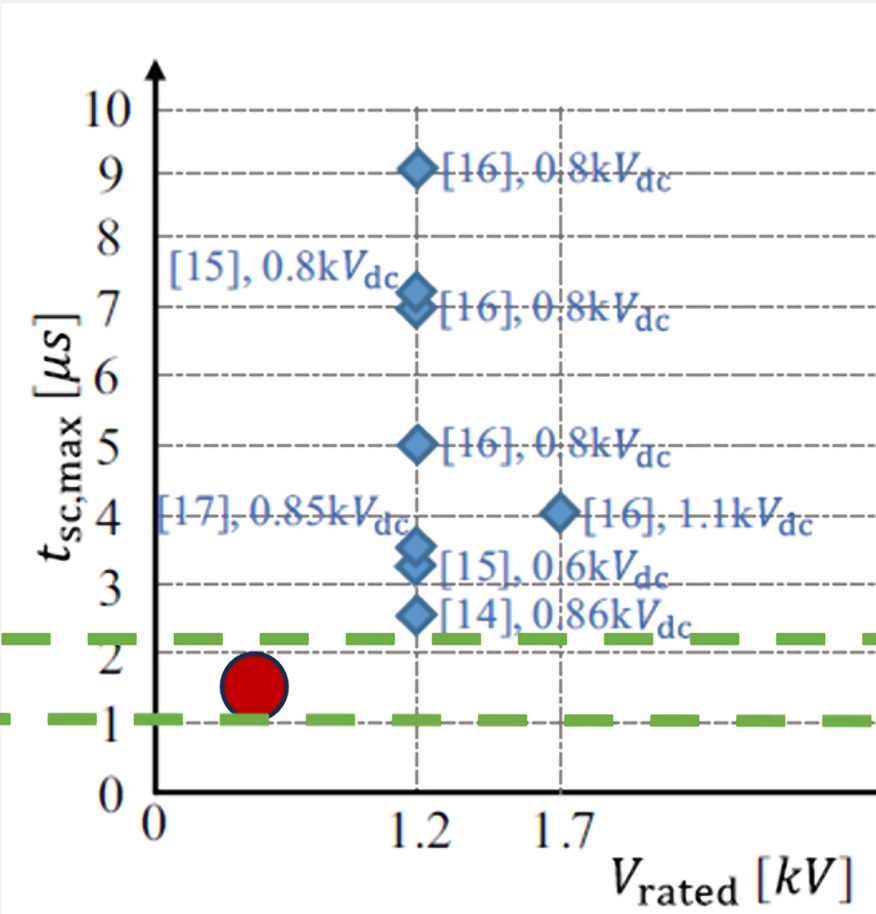

The short-circuit protection implemented in the driver should have a response time significantly faster than the maximum shortcircuit withstand time of the SiC device. Figure 6, below, summarizes the maximum short-circuit response time of SiC modules as a function of their rated drain-to-source voltage with the indicated DC-link voltage under test. A short-circuit response time below 2 μs is relatively safe for a single short-circuit event. Generally, short-circuit withstand time increases with larger device area and MOSFET channel length.6

The shorter the short-circuit response time, the greater the device’s ability to withstand multiple short-circuit events. However, there is no universally fixed value for short-circuit withstand time; it varies depending on factors such as voltage bus, package-die characteristics, and die area. For example, a SiC MOSFET in a TO-247 package has a short-circuit withstand time of 1.7 μs at 800 V and approximately 10 μs at 400 V.

Figure 7 summarizes the failure time of different types of power transistors versus DC bus voltage. Note that E-mode GaN HEMT failure times are much smaller than those for Si and SiC MOSFETs.

The measured short-circuit withstand time of a 650 V GaN, operating at DC voltage bus of 400 V is about 630 nsec.

The short-circuit withstand time can be calculated using the critical energy (Ec):

Figure 5: Short-circuit current comparison of the 1200 V/40 A SiC MOSFET and 1200 V/40 A Si IGBT under Vds = 600 V and Tc = 25°C4

Figure 6: Short-circuit response time (SCRT) of SiC modules

Figure 7: Failure time of different types of power transistors

Typical SiC MOSFET short-circuit behavior

Figure 8 shows the typical short-circuit waveforms of a low-inductance non-destructive test. A planar SiC 1200 V, with a DC bus limited to 400 Vdc, undergoes a low inductance (60 nH) short-circuit test using a 2.2 μs short-circuit pulse to ensure the device’s survival. The waveforms can be viewed in four phases:

- Phase A: The SiC MOSFET transitions from the cutoff region to the ohmic region. The current starts to rise rapidly due to the small loop inductance. In this case, the di/dt is about 4 A/ns, resulting in a current of up to 1 kA within 1 μs. At 1.1 μs, at the end of Phase A, the short-circuit energy is about 0.4 J, which exceeds the maximum dissipation limit of the device. Therefore, the shortcircuit

protection should be activated before the device enters the saturation region. - Phase B: The SiC MOSFET enters the saturation region, and the short-circuit energy continues to increase.

- Phase C: The SiC MOSFET remains in the saturation region. The increase in Rds,on results in a drop in Id from its peak.

- Phase D: When the SiC MOSFET is switched off (when the protection is activated), the high dI/dt (33 A/ns) induces a peak

voltage overshoot of 2.2 kV.

Short-circuit protection should be activated within the green (linear) region, typically within a 1-2 μs timeframe. When the short circuit is detected, the MOSFET should be switched off with a controlled slew rate (soft-switch feature) to minimize the overshoots.

Figure 9, below, illustrates the withstand time of 700 V Microchip planar SiC MOSFETs as a function of the gate-to-source voltage and DC voltage bus. As expected, the withstand time increases when Vgs is reduced. Allowing better control of the SiC MOSFET’s turnoff after short-circuit detection to minimize overshoot (soft-turnoff). One notable application where the superior withstand time of Microchip planar SiC MOSFETs is highly valuated is in solid-state circuit breakers (SSCBs) or E-fuses.8

Figure 8: Typical SiC MOSFET short-circuit behavior7

Figure 9: Microchip SiC MOSFETs exhibit short-circuit withstand times between 3 μs to 14 μs, depending on DC link voltage and applied Vgs

DESAT protection circuit9

A desaturation (DESAT) circuit is a widely used method for overcurrent and short-circuit protection in IGBT circuits. It works by monitoring the drain-to-source voltage when the device is fully on and automatically shuts it off if a short circuit or overcurrent event is detected.

Isolated gate drivers with built-in DESAT circuits, originally designed for IGBTs, can also be used with SiC MOSFETs and GaN devices.

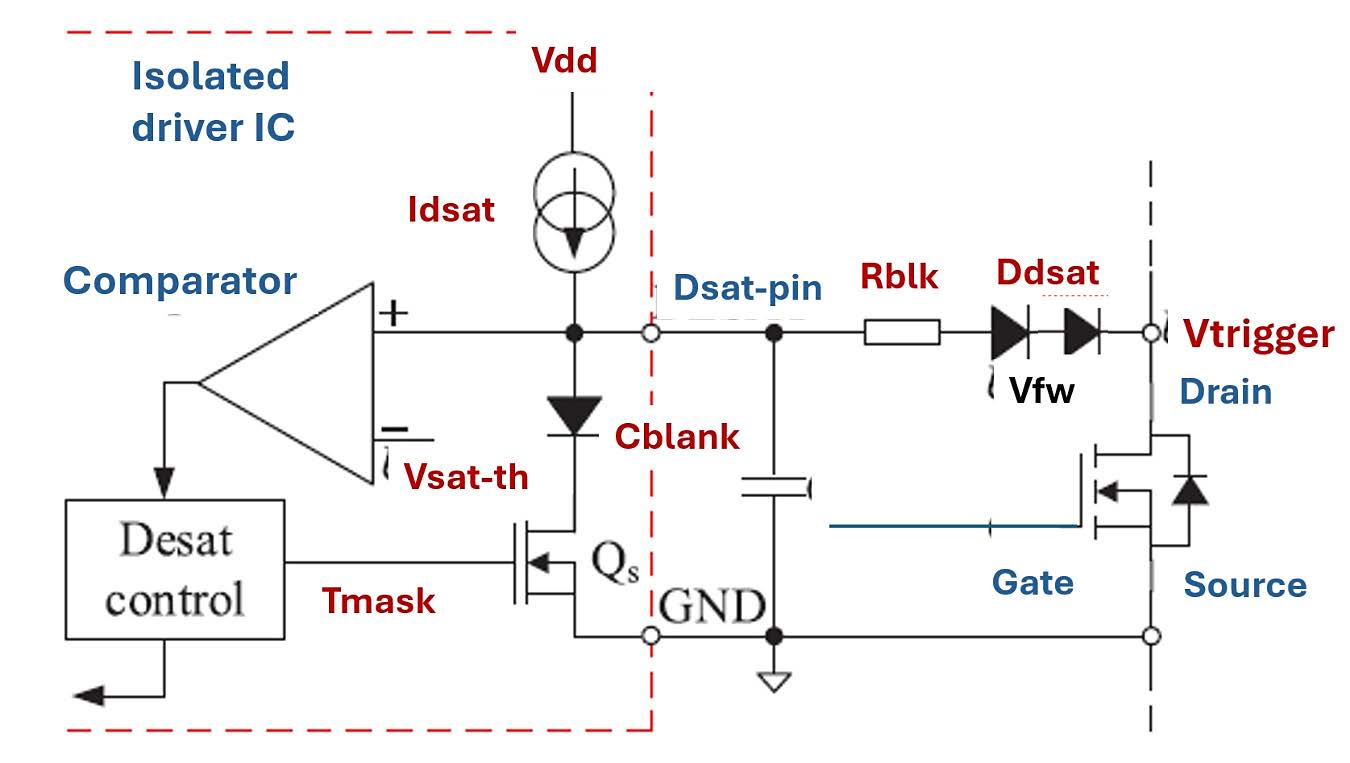

Typically, as shown in Figure 10, the DESAT circuit is integrated into the gate driver, requiring only a few external components—a fast high-voltage diode (Ddsat) or multiple diodes in series, a blanking capacitor (Cblank), and a resistor (Rblk).

When the MOSFET turns on, a current source (Idsat) charges the capacitor, creating a blanking period to prevent false triggers during switching. The diode becomes forward-biased once the capacitor voltage matches the MOSFET’s drain-to-source voltage. A short circuit is triggered when the MOSFET’s drain-source voltage (Vds) reaches the protection threshold (Vth-dsat), minus the forward voltage drop of the diode and the voltage across the series resistor (Idsat × Rdsat).

Figure 10: Typical DESAT protection circuit commonly used in gate drivers for IGBTs and SiC MOSFETs to protect against overcurrent and short-circuit conditions

Adjusting the resistor value or using multiple diodes in series can modify the trigger voltage.

Typically, the DESAT trigger point is set to twice the maximum peak current, but it should be carefully adjusted to the maximum desired current during a short-circuit event.

The DESAT diode must be a fast-recovery type with low junction capacitance to minimize noise susceptibility caused by rapid voltage changes (dv/dt).

The blanking time is configured to prevent false triggering during the MOSFET’s turn-on phase and to allow turn-on oscillations to settle. Both the trigger voltage (Vtrigger) and the blanking time should be fine-tuned based on the specific characteristics and turnon behavior of the SiC MOSFET.

It is critical to ensure that the total energy during a short-circuit event remains below one-fourth of the maximum withstand energy specified by the SiC manufacturer.

The DESAT circuit is simple, easy to implement, and has minimal power loss. However, it presents certain challenges when used with SiC MOSFETs. The forward diode must withstand high voltages and respond quickly, and the fixed blanking time can delay the short-circuit

protection response.

It is important to note that the DESAT method may not provide consistent accuracy across all fault conditions. Different fault scenarios, such as hard-switching faults or faults under load, can result in varying response times. Nonetheless, the primary objective is to prevent catastrophic device failure, even in the presence of low-inductance, rapid current surges.

For perspective, when protecting a typical SiC module, a mere 0.5 V variation in the DESAT threshold voltage can correspond to a difference of up to 100 A in drain current.

Fault response time for SiC MOSFETs

The short-circuit response time (SCRT) should be limited to 1 μs for SiC MOSFETs. The total protection response time, as illustrated in Figure 11 is the sum of four components:

- t_mask: A fixed time during which the DESAT pin is intentionally held low (connected to ground) to prevent false triggering of the protection circuit due to voltage spikes during the initial turn-on of the SiC MOSFET. This time is typically set between 200–300 ns.

- t_blank: The charging time of the C_blank capacitor through the internal current source or an external resistor.

- t_filter: The typical internal delay between the DESAT voltage reaching its threshold and the issuance of the turnoff command to the MOSFET’s gate.

- t_soft: The soft shutdown time, which is added to reduce the risk of overvoltage spikes during the SiC MOSFET’s turnoff process.

The waveform shown in Figure 12, below, was captured on a bench during a hard-switched fault scenario, where the MOSFET is turning on into a fault condition. In this case, the blanking time adds the total fault detection time, followed by the ramp time, which is typically defined by a pull-up resistor charging an external capacitor. This ramp continues until the voltage reaches the threshold, triggering the soft shutdown sequence.

The bottom yellow trace shows the gate-to-source voltage rising, and when the short-circuit protection is activated, it transitions into soft shutdown mode.

As mentioned earlier, the total reaction of the DESAT circuit should be within 1–2 usec. To speed-up the detection time without compromising the noise immunity of the Dsat pin, it is possible to increase the internal charging current of the Cblank capacitor by

adding external current source. To maintain a good noise immunity, the Cblank capacitor should have a value above 300 pF.

Figure 13 shows the external circuitry configuration that can be used to obtain a faster charging time for the Cblank capacitor, without reducing its capacitance value. This solution can also be implemented for cascode GaN devices, enabling a total response time below 400 ns.12

Figure 14, below, shows a discrete short-circuit protection circuitry optimized for fast detection and protection, specifically designed and tested for GaN HEMT devices. This circuit has been tested with a total response time of 122 ns.13

The basic principle is to measure Vds-on across the device in its on-state (Vsense) and compare it to a reference voltage. If Vsense exceeds Vref, the comparator provides a high fault signal (FLT). The turn off signal is used to reset the Vsense voltage.

If an isolated driver is used, the FLT signal can be sent back to the driver though an isolator. The FLT signal to the driver can disable the gate driver, forcing a hard turnoff of the GaN device. Isolated drivers with short propagation delay are preferable for achieving ultrafast response times.

Figure 11: Total protection response time

Figure 12: Hard switch fault scenario of a SiC module with isolated gate driver from Analog Devices.11 The total response time is kept below 1 μs.

Figure 13: External circuitry configuration for faster charging time for the Cblank capacitor, without reducing capacitance value

Figure 14: Ultrafast response time for GaN HEMT devices13

Gate current requirements and power dissipations

To achieve the desired switching speed, it is essential to choose a gate driver with an appropriate drive current capacity.

The peak source and sink current can be easily calculated by dividing the voltage applied across the gate-to-source terminal (dVgdr) by the sum of the resistances path:

Rgin represents the internal gate resistance of the SiC MOSFET, Rgonext and Rgoffext are the external gate resistors used to control the turn-on and turnoff speeds. Similarly, Rgondriver and Rgoffdriver denote the internal resistance of the gate driver.

To ensure that the external resistors can effectively regulate the switching speeds, the source and sink current remain within the driver’s peak current limits.

To improve heat dissipation and boost gate peak current in high-frequency or high-current SiC applications, an external totem pole bipolar transistor is recommended.

Figure 15, below, illustrates a basic drive enhancement circuit for the Si828x isolated driver from Skyworks. Bipolar transistors Q1 and Q2 regulate the driver current, controlled by the VH and VL signals. The image on the right illustrates a peak source current of up to 30 A with a gate capacitance of 220 pF.

Especially in large module applications, the external totem pole circuit helps optimize layout and performance by allowing the transistors to be placed closer to the MOSFET gate. This minimizes gate circuitry inductance and reduces potential ringing at the device’s gate pin. Moreover, the external circuit prevents exceeding the driver’s maximum power dissipation capability.

The total power requirement of the gate circuitry is determined by multiplying the total gate charge (Qg) of the SiC MOSFET by the voltage applied across the gate-to-source terminal (dVgdr) and the switching frequency (fsw):

Conclusion

Overall, the continuous advancements in isolated gate driver technology are essential for the successful integration of WBG devices in various applications, paving the way for more efficient and reliable power electronics systems.

References

(*1) AN583 Safety Considerations and Layout Recommendations for Digital Isolators – Skyworks

(*2) ND90204 EliteSiC Gen 2 1200V MOFETs application note – ONSEMI

(*3) Peak Current of Isolated Gate Driver – Analog Devices

(*4) Review and analysis of SIC MOSFET’s ruggdness and reliability – Jun Wang, Xi Jiang – Feb 2020

(*5) AN5355 Mitigation techniques of the SIC MOSFET gate voltage glitches with Miller clamp

(*6) Comparison and Discussion on Short-circuit Protection for SiC MOSFET Modules, Slavko Mocevic IEEE

(*7) Source: New definition of critical energy for SiC MOSFET robustness under short circuit operation.

(*8) SiC-Based Auxiliary E-Fuse Technology Demonstrator for EV Applications – Microchip – PCIM Europe

(*9) AN1288: Si828x External Enhancement Circuit – Skyworks An improved desaturation short-circuit protection method for SiC power modules science direct

(*10) An improved desaturation short-circuit protection method for SiC power modules science direct (CPESE 2021)

(*11) Wolfspeed- Analog Device – Isolated Gate driver seminar

(*12) AN1288: Si828x External Enhancement Circuit- Skyworks

(*13) A Simple Desaturation Based Protection Circuit for GaN HEMT With Ultrafast response time – IEEE June 2021

(*14) AN1288 Si828x External Enhancement Cicuit – Skyworks DN80 – Bipolar transistors for MOSFET gate driving applications – Diodes